# Design, implementation, and performance analysis of the WorldFIP/ATM local bridge

Tuncay AYDOĞAN<sup>1,\*</sup>, İbrahim ÖZÇELİK<sup>2</sup>, Akif KUTLU<sup>1</sup>, Hüseyin EKİZ<sup>3</sup>

<sup>1</sup>Faculty of Technical Education, Süleyman Demirel University, Isparta-TURKEY

e-mails: tuncayaydogan@sdu.edu.tr, akifkutlu@sdu.edu.tr

<sup>2</sup>Faculty of Engineering, Sakarya University, Sakarya-TURKEY

e-mail: ozcelik@sakarya.edu.tr

<sup>3</sup>Faculty of Technical Education, Sakarya University, Sakarya-TURKEY

e-mail: ekiz@sakarya.edu.tr

Received: 22.10.2010

#### Abstract

World factory instrumentation protocol (WorldFIP) is a fieldbus network protocol that provides a link between level zero (sensors/actuators) and level one (field controllers such as programmable logic controllers, etc.) in industrial automation systems. Accessing and connecting the WorldFIP remotely is important for monitoring, maintaining, and controlling devices in a factory in which asynchronous transfer mode (ATM) is used as a backbone network. In this study, a transparent WorldFIP/ATM bridge was designed and implemented in order to access devices on WorldFIP via an ATM network. This designed bridge may also provide control of the devices over wide area networks. The bridge's performance was investigated using network simulation software under various message traffic conditions. The results obtained from the simulations showed that the bridge provides real-time communications between WorldFIP and ATM.

Key Words: WorldFIP, ATM, bridge, industrial communications, fieldbuses

#### 1. Introduction

The computer-integrated manufacturing (CIM) model shows the hierarchical architecture of a communication network in a factory plant. The CIM model is divided into 5 layers. The lowest level, level 5, is the fieldbus network that consists of sensors and actuators. The highest level, level 1, is wide area network that includes mainframes [1]. Data are exchanged between the lowest and the highest levels of these communication layers. Communication devices for each of these layers may be far away from each other and use different communication network technologies.

Although standard computer networks have 7 layers of the open systems interconnection (OSI) model, fieldbus networks have only 3 layers. These include a physical layer, a data link layer (implicitly including the media access control layer), and an application layer [2].

<sup>\*</sup>Corresponding author: Faculty of Technical Education, Süleyman Demirel University, Isparta-TURKEY

Fieldbus networks connect field devices such as sensors, actuators, field controllers such as programmable logic controllers (PLCs), regulators, drive controllers and man-machine interfaces [2]. There are several fieldbus network systems, including ASI, BITBUS, CAN, DeviceNet, Hart, IEC-Fieldbus, InterBus-S, LonWorks, P-NET, PROFIBUS, Rackbus, SECROS, SDS, TRON, and world factory instrumentation protocol (WorldFIP) [1]. All of them have real-time communications specifications.

Real-time requirements for fieldbus systems' message latency times are 100-300 ms in process technology, 10-100 ms in manufacturing technology, and 1-10 ms in drive systems [3]. In another study, response times of fieldbuses were 10 ms at 34%, 1 ms at 30%, 100 ms at 14%, >100 ms at 12%, and 0.1 ms at 10% [4].

Remote real-time connections to fieldbuses are important as they are necessary for monitoring, maintaining, and controlling operations within the factory environment [2,5,6]. Earlier research developed solutions for remote interconnection between the fieldbus and upper layers of CIM, Ethernet [7,8], fiber distributed data interface (FDDI) [9], and asynchronous transfer mode (ATM) [5,6,10-12]. These solutions demonstrated that real-time communications specifications with ATM can be provided. They also showed that ATM can support traffic from various types of real-time applications over a large distance while guaranteeing communications latency and bandwidth available to the user applications [13-16].

In order to make connections between different network systems, devices that translate the complete protocol stack from one system to another are used [1]. If different networks including all OSI layers are being used, a gateway device is used. However, if there is only a single path possible between stations, the network layer is not necessary. In that case, a bridge device is used to connect networks. Fieldbuses do not need a network layer. Thus, they can be interconnected with bridges [2,17]. In the literature, there are approaches with both gateways and bridges [5,6,18-20]. In these papers, bridges, WorldFIP, and ATM were not researched at the same time for real-time connections to remote fieldbuses.

WorldFIP has been controlled and monitored over/on ATM by using a PC gateway [21]. In contrast to previous research, the present study used ATM as a backbone since ATM is suitable for WorldFIP [13]. Furthermore, a bridge was designed and implemented between the WorldFIP fieldbus and ATM in order to connect to the WorldFIP remotely.

The rest of the paper proceeds as follows. First, brief information about WorldFIP and ATM are given. Second, the design architecture of the WorldFIP/ATM bridge and its algorithm are presented. Finally, the performance analysis of the WorldFIP/ATM bridge is discussed.

#### 1.1. WorldFIP

WorldFIP is a fieldbus that is used in industry, power, process, and transport [22-25]. It is described in Volume 3 of EN50170, which is the first international industrial communication standard to also become a standard in all western European countries. WorldFIP has a 3-layered fieldbus architecture. The physical layer of WorldFIP provides data transmission at S1 (31.25 kbit/s), S2 (1 Mbit/s), and S3 (2.5 Mbit/s) on shielded twisted pair (STP) and at 5 Mbit/s on fiber optics. The data link layer provides transmission services of variables and messages. The application layer provides periodic/aperiodic message transmission services [26,27].

The WorldFIP network structure consists of a bus and stations with a bus arbitrator (BA) and producer/consumer specifications. The BA controls the bus and other stations with medium allocation mechanisms including periodic transfer, request for aperiodic transfer, and unacknowledged and acknowledged aperiodic message transfer requests. All network schedules are provided by a saved bus arbitrating table (BAT). The BAT

includes all defined variables and their timings. The BA cycles orderly microcycles and macrocycles for them. Variables enable the producer or consumer to connect with other stations. When producer stations receive their own producer variables, they create a message including data that is received from the sensor and is sent to consumer stations. When consumer stations receive their own consumer variables, they receive the message, including the data, and subsequently activate their own actuators from producers. All of these are provided by 6 types of frame. The chips used for these functions are FULLFIP2, MICROFIP, FIELDDRIVE, and FIELDDUAL. This mechanism is detailed extensively in the literature [24,25,27-29].

#### 1.2. ATM

ATM is a communication technology that has transport, switching, network management, and customer services. The transport of data is provided by 53-byte fixed-length packets called cells by packet switching technology. Transport is both continuous bit rate (CBR) and variable bit rate (VBR). ATM switching is performed by routing the incoming virtual path and virtual channel identifiers (VPI/VCI) and using a hardware-based look-up table. Before data are sent, an ATM network establishes a "connection" by permanent virtual channels (PVC) or switched virtual channels (SVC). The ATM adaptation layer (AAL) adjusts the transfer process to perform the upper layer services required by different users. There are 4 types of AAL (AAL1, AAL2, AAL3/4, and AAL5 are defined as 4 types). AAL3/4 provides the transport of error-detected variable-length frames via connection-oriented and connectionless services. Other specifications are detailed in [30,31].

## 2. Designing and modeling of WorldFIP/ATM bridge

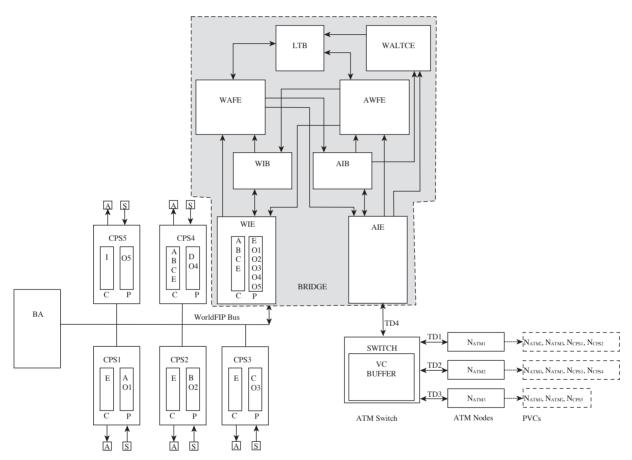

Figure 1 shows a block diagram of the whole system. The system consists of a designed WorldFIP network model, an ATM network model, and a designed WorldFIP/ATM bridge. Both networks produce traffic. In this paper, the term "frame" is used for a message of WorldFIP, "cell" for a message of ATM, "local (L)" for inner network traffic, and "remote (R)" for outer network traffic. The Table shows L/R messages and transmission links of nodes of both the WorldFIP and ATM networks.

| Nodes   |      | Receivers |      |      |      |      |      |      |      |

|---------|------|-----------|------|------|------|------|------|------|------|

|         |      | ATM1      | ATM2 | ATM3 | CPS1 | CPS2 | CPS3 | CPS4 | CPS5 |

| Senders | CPS1 |           |      | R    |      |      |      | L    |      |

|         | CPS2 | R         |      |      |      |      |      | L    |      |

|         | CPS3 |           | R    |      |      |      |      | L    |      |

|         | CPS4 |           |      |      |      |      |      |      | L    |

|         | ATM1 |           | L    | L    | R    | R    |      |      |      |

|         | ATM2 | L         |      | L    |      |      | R    | R    |      |

|         | ATM3 | L         | L    |      |      |      |      |      | R    |

Table. Transmission links of nodes of WorldFIP and ATM networks.

## 2.1. Design and modeling of the WorldFIP network

The WorldFIP network consists of a bus and 6 nodes (called a station), which are a BA and the  $N_{CPSn}$ . They have consumer (C) or producer (P) characteristics (see Figure 1), respectively. An actuator (A) and a sensor (S) are connected to each C/P node. The nodes are enabled as consumers or producers by the identifiers labeled

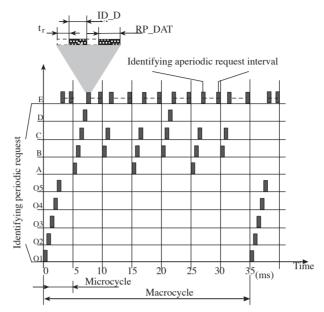

as A, B, C, D, and E. The A, B, C, and D identifiers are for data transmission. O1-O5 identifiers are for the learning process of the bridge. The E identifier is for aperiodic transmission requests. Frame producing is provided by D and E as local, O1-O5 as remote, and A, B, and C as both remote and local. Thus, the local and remote traffics in the Table are generated by identifiers. When a node receives an identifier that enables it as a consumer, the node then expects a frame consisting of data. However, when a node receives an identifier that enables it as a producer, the node will send a frame consisting of data. For example, A, B, C, and E identifiers enable  $N_{CPS4}$  as a consumer, and D and O4 identifiers enable it as producer. As an additional example, when  $N_{CPS1}$  receives A, it produces a data frame.  $N_{CPS4}$  subsequently receives this frame as a consumer. This traffic of identifiers is provided by the BAT configurations shown in Figure 2.

Figure 1. Block diagram of designed system.

The scheduling of the BAT in Figure 2 consists of 2 parts: an elementary interval called a "microcycle" and a whole cycle interval called a "macrocycle," which contains 7 microcycles. The BAT organizes the transfer of identifiers in order. As Figure 2 shows, the BA orderly sends O1, O2, O3, O4, O5, A, B, C, D, and E identifiers to the bus at the beginning of each microcycle. O1, O2, O3, O4, and O5 identifiers are sent at the first microcycle; A, B, C, and D identifiers at the second microcycle; B and C identifiers at the third microcycle, and so on. These cycles are regularly repeated at each macrocycle. The BA also sends padding frames at idle time intervals. The whole above process cycle is called a "periodic" communication type.

Figure 2. BAT of designed WorldFIP network model.

When BAT scheduling works as planned, messaging requirements may emerge from any node suddenly. First, these messaging requirements are queued in the WorldFIP interface buffer (WIB), and then the messaging occurs with the E identifier in a padding time interval by the BA. This is called an "aperiodic" communication type.

Messages received from ATM are aperiodic. Aperiodic messaging is therefore considered in the WorldFIP network modeling.

Message traffic is modeled for A, B, C, D, and E identifiers as unacknowledged and for O1, O2, O3, O4, and O5 identifiers as acknowledged message transfer requests.

The BA and whole stations apply all of these algorithms [26-29].

Buffer transfer time (C) is the elementary transaction time of the transmission of a pair of frames: ID\_DAT, followed by an RP\_DAT [27]. Buffer transfer time is calculated using the following formula.

$$C = \frac{len(ID\_DAT) + len(RP\_DAT)}{bps} + 2 \times tr$$

(1)

The elementary transaction time of modeling the WorldFIP network is calculated with a 64-bit ID\_DAT frame, RP\_DAT having at most 1072 bits; the network data rate is 2.5 Mbit/s (S3) and tr = 20  $\mu$ s.

Hence, we calculated and used:  $C = \frac{64+1072}{2.5} + 2 \times 20 = 494.4 \approx 495 \mu s$ .

Finally, the WorldFIP bus and nodes were modeled according to S3 and the specifications of FULLFIP2, MICROFIP, FIELDDRIVE, and FIELDDUAL 80-MHz chips.

#### 2.2. Design and modeling of ATM network

An ATM network comprises  $N_{ATM1}$ ,  $N_{ATM2}$ , and  $N_{ATM3}$  user points, a switch, and the buses of their interconnections, as shown in Figure 1.

It is assumed that ATM nodes communicate using a PVC and are composed of virtual connections (VC), as shown in the Table. ATM nodes produce local and remote message cells. They control the message identifier's

(MID) field of received messages. If message cells come back to the source, ATM nodes acknowledge them and send an acknowledged message cell to the switch. Based on the content of the VC table, the switch sends ATM message cells and WorldFIP remote messages. It also composes and updates VCs using the acknowledged messages.

Network data transfer rates for TD1, TD2, and TD3 buses are modeled as 25 Mbit/s, and for TD4 as 155 Mbit/s in the IBM 8285 Nways Workgroup Switch [32].

## 2.3. Designing and modeling of bridge entities

Entities of the bridge shown in Figure 1 were designed and modeled as described below.

- The WIB is a memory that has 2 subdivisions to save forwarding frames from the ATM to the WorldFIP and vice versa. Thus, it is a structure increasing bridge performance as it provides forwarding in either direction at the same time. The structure of the first side of the memory map has 256-byte RP-MSG-xx frames, while the other side has 44-byte AAL3/4 cells. Memory is modeled at a 25-ns data read/write rate and a first-in, first-out (FIFO) stack.

- The ATM interface buffer (AIB) is a memory with 2 forwarding cells, from the ATM to the WorldFIP and vice versa. The length of each side of the memory map is structured according to 44-byte AAL3/4 cells. Memory is modeled at a 25-ns data read/write rate and a FIFO stack.

- The look-up table buffer (LTB) is a database that has addresses and connection information of nodes according to forwarding processes from the WorldFIP to the ATM. The LTB's database is composed of the VPI/VCI of the ATM header and the physical address of WorldFIP frames. This information is updated by the look-up-table composing entity from the WorldFIP to the ATM (WALTCE). The memory data read/write rate is modeled at 25 ns.

- The WorldFIP interface entity (WIE) is the WorldFIP bridge port. First it receives all messages from the WorldFIP bus. It subsequently filters local messages and writes others in the WIB. Thus, it blocks unnecessary loads on the bridge. It also reads messages from the ATM to WorldFIP and queues them in the WIB, and sends them to the WorldFIP bus at aperiodic time intervals. Lastly, it sends acknowledged messages to the ATM interface entity (AIE). Its structure has a WorldFIP station modeled as an 80-MHz FULLFIP2 chip.

- The AIE is an ATM bridge port. First it receives whole cells from the switch and writes to the AIB. It also restructures the header of cells. It then reads messages from the WorldFIP to the ATM and queues them in the AIB, then sends them to the switch. Lastly, it sends acknowledged messages from the switch to WALTCE. Its structure is modeled as a 16-MHz 8051-based chip comprising a cell delineation block (CDB) and SOT-3. The CDB has functions of a transmission convergence (TC) sublayer on the ATM physical layer.

- The forwarding entity from the WorldFIP to ATM (WAFE) reads related fields of queued messages from the WorldFIP to the ATM in the WIB, and then it compares them with the LTB. It converts from WorldFIP frames to ATM AAL3/4 cells and writes to the AIB. Its structure is modeled as a 16-MHz 8051-based chip.

- The forwarding entity from the ATM to WorldFIP (AWFE) reads queued messages from the ATM to the WorldFIP in the AIB, and then it converts to WorldFIP frames and writes to the WIB. Its structure is modeled as a 16-MHz 8051-based chip.

- WALTCE writes and updates related fields of learning messages from the WorldFIP to the ATM to the LTB. Thus, the bridge performs the learning process. It does not compose the LTB from the ATM to WorldFIP, because it is performed on a VC by a switch. Its structure is modeled as a 16-MHz 8051-based chip.

- The WorldFIP data bus (WDB) and ATM data bus (ADB) are used for data transmission between entities and buffers in the modeled bridge. The WorldFIP signaling bus (WSB), ATM signaling bus (ASB), and WorldFIP-ATM signaling bus (WASB) are used to control signal transmission interentities.

## 2.4. Algorithms of bridging functions

Figure 3 shows that the bridge is an abstracted algorithm of frame/cell receiving, learning, and forwarding functions for each protocol. These functions are performed using LTB and VC. Processing of remote messages is performed with forwarding algorithms. In addition, the composing process of the empty LTB and VC at start-up is performed with learning algorithms.

Figure 3. Abstract flowchart of bridging functions.

Forwarding algorithms are based on the following 4 steps.

- 1) The WIE receives whole messages from the WorldFIP bus and then filters local ones.

- 2) The WAFE converts from WorldFIP frames to ATM AAL3/4 cells and forwards to the ATM side by following substeps b1, b2, and b3.

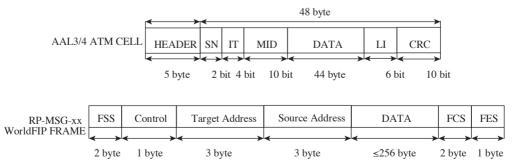

Figure 4. Structure of AAL3/4 ATM cell and WorldFIP frame.

Figure 4 shows the WorldFIP frame and different structures of the AAL3/4 ATM cell. The frame has a variable data length of up to 256 bytes and destination and source addresses. However, the cell has only 44 bytes of data and does not have target or source addresses. Instead of addresses, the cell has VPI/VCI fields. Bridges discard idle fields and reform frame formats on these dissimilar structures.

- b1) Discarding frame start sequence (FSS), control, frame check sequence (FCS), and frame ending sequence (FES) idle frame fields for the cell.

- b2) Reconstructing target, source, and data fields of frame to cell: data fields of up to 256-byte frame segmentation to 44-byte AAL 3/4 cell data fields. The length indicator (LI) field of the cell is then composed by the WAFE. Each address field of the frame consists of a 1-byte link service access point (L\_SAP), 1-byte physical address, and 1-byte segment address. It is assumed that the modeled WorldFIP network consists of only one segment, while the segment address and L\_SAP are idle for the ATM. Hence, the 1-byte (8 bits) physical address is placed in the 10-bit MID field in the ATM.

- b3) Producing new fields: There are no sequence number (SN), information type (IT), or cyclic redundancy check (CRC) fields of the cell in the fields of frame. These fields are recalculated and added to the cell by the AIE.

- 3) The AIE receives all cells from the switch.

- 4) The AWFE converts ATM AAL3/4 cells to WorldFIP frames and forwards to the WorldFIP side with substeps d1, d2, and d3.

- d1) Discarding SN, IT, LI, and CRC idle fields of the cell.

- d2) Reconstructing VPI/VCI and MID fields of the cell to the frame address by using the LTB: AAL3/4 cell data fields are moved to the frame data field by the AWFE.

- d3) Producing new fields: FSS, control, FCS, and FES fields are recalculated and added to the frame by the WIE.

Learning algorithms occur by the following 2 steps.

The learning of the bridge is the process of creating the LTB. According to the "static LTB," it is fixed at start-up. In the case of the "dynamic LTB," it is free at start-up and is then filled by learning algorithms [33]. The latter approach was used in this paper.

1) Learning algorithms of the WorldFIP side

WorldFIP nodes send RP-MSG-xx frames that do not have data to ATM nodes as learning messages at periodic cycles. They have O1, O2, O3, O4, and O5 identifiers and acknowledged message transfer requests.

At first, messages are received by the WIE.

The WAFE reads these messages and determines learning messages. Learning messages are then forwarded to the AIE and the switch. The forwarding algorithm is thus completed.

ATM nodes send acknowledgement messages back. An acknowledgment message is forwarded to the switch, AIE, and WALTCE updates related fields of the learning messages as writing into the LTB.

2) Learning algorithms of the ATM side

The ATM side has a VC table in the switch instead of the LTB. Remote messages of ATM nodes are forwarded to the other side by forwarding algorithms. The WorldFIP side sends an acknowledgment message back. Acknowledgement messages build up the VC table in the switch and update.

## 3. Analysis of model and simulation results

The designed model was simulated by the NETWORK II.5 simulation package. This package was created by the SIMSCRIPT II simulation programming language [34,35]. NETWORK II.5 can model low levels of OSI and realtime systems [5,6]. Therefore, it can be used for modeling the WorldFIP and ATM. Figure 5 shows the designed model of both the WorldFIP and ATM, and it also demonstrates the designed bridge between these 2 protocols.

Figure 5. Simulation model of designed system.

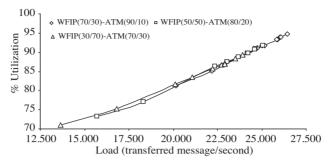

In the WorldFIP network simulation, the message traffic characteristic is defined with local-and-remote frame ratios of 70%/30%, 50%/50%, and 30%/70%, with frequency as exponential and the data field of frame as a random variable of up to 256 bytes. These loads are showed as WFIP(70/30), etc.

In the ATM network simulation, the message traffic characteristic is defined with a local-and-remote cell ratio of 90%/10%, 80%/20%, and 70%/30%, with frequency as exponential. The size of a cell is fixed as 53 bytes. These loads are showed as ATM(90/10), etc.

Performance analysis of the bridged system is carried out by means of bus utilization, process time, queued message number, delivery time, and entity utilization under various local/remote message traffics. These help us to explain the bridge's characteristics [5].

The utilizations of buses show the number of transferred messages and cells in a second (load) at various local-to-remote message ratios. Process time indicates the transmission time of the bridge's port-to-port message and cell under different loads. Process time is obtained from the delays caused by running the processes of each bridge entity. According to simulation results, the maximum number of the frames queued at the buffer implies the bridge's offered buffer capacity. The remote message/cell delivery time is the time required to complete a transformation of a frame from the WorldFIP node to the ATM node. Remote message delivery time is directly related to the bridge performance.

Figure 6 shows the utilization of the WorldFIP bus under different loads at various local-to-remote message ratios. As Figure 6 demonstrates, bus utilization changes between 71% and 94% with 13,626 and 26,444 frames of load. This high bus utilization is caused by the BA's padding in the periodic cycle.

Figure 6. The utilization of the WorldFIP bus.

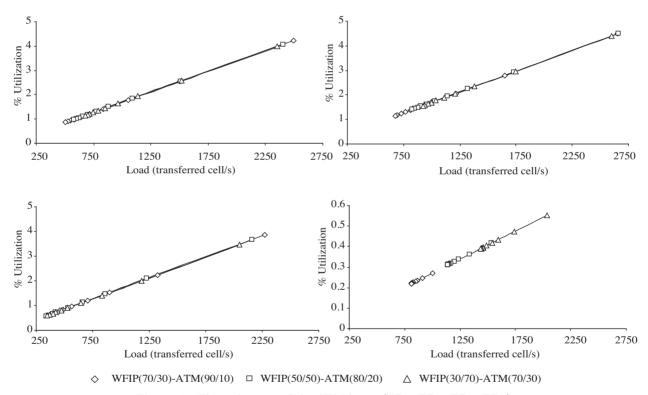

Figure 7 shows the utilization of the ATM buses. They are labeled as TD1, TD2, TD3, and TD4 under different loads at various local-to-remote message ratios. TD1, TD2, and TD3 utilization changes between 0.5% and 4.5% according to 341 and 2657 cells of load. Additionally, TD4 utilization has a variation between 0.2% and 0.5% by 812 and 2035 cells of load. These low bus utilizations are caused by the ATM buses' data rate, since it is very high and the size of the cell is small according to WorldFIP.

Figure 7. The utilization of the ATM buses (TD1, TD2, TD3, TD4).

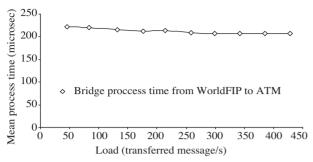

Figure 8 shows the bridge process time from the WorldFIP to ATM under different loads. The average process time changes between 206 and 221  $\mu s$  at loads of 342 and 46 frames.

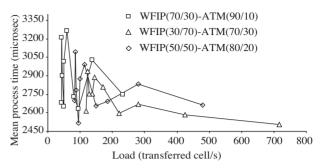

Figure 9 shows the bridge process time from the ATM to WorldFIP under different loads. The process time is calculated from 2.5 to 3.2 ms according to 718 cells under WorldFIP (30/70)-ATM (70/30) loads and 59 cells under WorldFIP (70/30)-ATM (90/10) loads. Messages that are going to be sent to the WorldFIP fieldbus are queued in the WIB until the BA's next periodic cycle, as described in Section 2.3. Deferral of this message transfer causes fluctuation of the processing time.

Figure 8. Bridge process time from WorldFIP to ATM.

Figure 9. Bridge process time from ATM to WorldFIP.

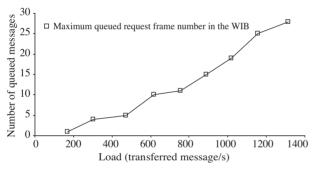

Figure 10 shows the maximum queued request frame number in the WIB from the WorldFIP to ATM under different loads, as in Figures 6 and 7. The maximum queued frame number is 28 at 1314 frames of load. Thus, the capacity of the WIB should be a minimum of 28 frames. The capacity of the WIB is greater than that of the AIB. This is caused by messages waiting until the BA's periodic cycle in the WIB.

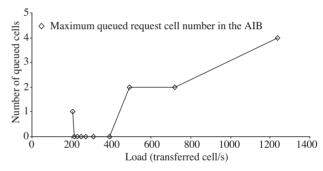

Figure 11 shows the maximum queued request cell number in the AIB from the ATM to the WorldFIP under different loads, as in Figures 6 and 7. The maximum queued cell number is 4 at 1239 cells of load. Thus, the capacity size of the AIB should be a minimum of 4 ATM request cells.

Figure 10. Maximum queued request frame number in the WIB.

**Figure 11.** Maximum queued request cell number in the AIB.

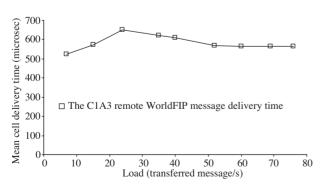

Figure 12 shows the labeled C1A3 (from CPS1 to ATM3) remote WorldFIP message delivery time from the WorldFIP to ATM. The delivery time varies from 523 to 650  $\mu$ s, varying between 7 and 24 frames of load.

Figure 12. The remote WorldFIP message delivery time.

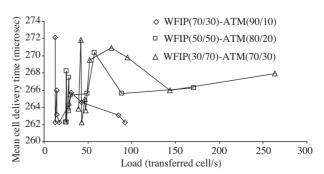

Figure 13. The remote ATM message delivery time.

Figure 13 shows the labeled A3C5 (from ATM3 to CPS5) remote ATM message delivery time from the ATM to WorldFIP. The delivery time varies from 262 to 272  $\mu$ s at variation under WorldFIP (70/30)-ATM (90/10) loads.

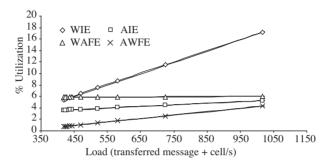

Figure 14 shows the utilization of the bridge entities under WorldFIP (30/70)-ATM (70/30) loads. The utilization varies from 5.5% to 17% for WIE, is 6% for WAFE, varies from 3.6% to 5.5% for AIE, and varies from 0.7% to 4.3% for AWFE. The usage rate increases when the load increases.

Figure 14. The utilization of bridge entities.

## 4. Conclusion

In this study, a transparent and translating WorldFIP/ATM bridge was designed between a WorldFIP fieldbus and an ATM network. The designed architecture was modeled and the performance analysis of the bridge was investigated.

In the design and implementation stages, WorldFIP and ATM technical specification was considered. The bridge was modeled and analyzed using discrete event simulation technique tools.

The results of the analysis showed that the bridge process time from the WorldFIP to the ATM varied from 206 to 221  $\mu$ s, and varied from 2.5 to 3.2 ms from the ATM to WorldFIP under different loads. The maximum queued frame number was 28 frames in the WIB and 4 cells in the AIB. The C1A3 remote WorldFIP message frame delivery time was 523-650  $\mu$ s from the WorldFIP to ATM. The A3C5 remote ATM message cell delivery time was 262-272  $\mu$ s from the ATM to WorldFIP. Finally, the utilization of the bridge entities was 5.5%-17% for WIE, 6% for WAFE, 3.6%-5.5% for AIE, and 0.7%-4.3% for AWFE.

Based on these results, latency times of 1-10 ms for drive systems and 10-ms response times at 34% of the fieldbus are supported by our research. In other words, the WorldFIP/ATM bridge provides real-time requirements for fieldbus systems. This means that the system can be utilized to monitor, maintain, and control the WorldFIP fieldbuses through ATM networks using a designed bridge.

## References

- [1] G. Schickhuber, O. McCarthy, "Distributed fieldbus and control network systems", Computing & Control Engineering Journal, Vol. 8, pp. 21-32, 1997.

- [2] J.P. Thomesse, "Fieldbus technology in industrial automation", Proceedings of the IEEE, Vol. 93, pp. 1073-1101, 2005.

- [3] K. Etschberger, Controller Area Network, Weingarten, IXXAT Press, 2001.

- [4] W. Lawrenz, CAN System Engineering from Theory to Practical Applications, New York, Springer-Verlag, 1997.

- [5] İ. Özçelik, H. Ekiz, "Design, implementation and performance analysis of the PROFIBUS/ATM local bridge", Computer Standards & Interfaces, Vol. 26, pp. 329-342, 2004.

- [6] İ. Özçelik, H. Ekiz, "Design, implementation and performance analysis of the CAN/ATM local bridge", Computer Standards & Interfaces, Vol. 30, pp. 177-186, 2008.

- [7] F. Arjmandi, B. Moshiri, "Fieldbus interoperability on ethernet", Industrial Informatics, 5th IEEE International Conference, Vol. 1, pp. 213-218, 2007.

- [8] G.Y. Li, J. Xu, "An approach for fully integrated automation in heterogeneous industrial control network", ICICTA: Second International Conference on Intelligent Computation Technology and Automation Proceedings, Vol. 3, pp. 7-10, 2009.

- [9] S. Cavalieri, A. Di Stefano, O. Mirabella, "Exploiting FDDI communication features to connect fieldbuses in process control environment", Local Computer Networks Proceedings, pp. 59-66, 1994.

- [10] O. Kunert, "Interworking between independent PROFIBUSes through ATM networks", Broadband Communications Proceedings, pp. 147-154, 2000.

- [11] İ. Özçelik, H. Ekiz, "Building an interconnection between PROFIBUS and ATM networks", Journal of Network and Computer Applications, Vol. 30, pp. 800-817, 2007.

- [12] C. Cseh, M. Janssen, J. Jasperneite, "ATM networks for factory communication", Emerging Technologies and Factory Automation 7th IEEE International Conference Proceedings, Vol. 2, pp. 797-804, 1999.

- [13] T. Wijnands, W. Herr, P. Ribeiro, "A prototype ATM network for real time control of the LHC", ICALEPCS'99, pp. 176-178, 1999.

- [14] I. Mizunuma, C. Shen, M. Takegaki, "New architecture of industrial systems with real-time ATM middleware", Third International Workshop on Real-Time Computing Systems Application, pp. 246-253, 1996.

- [15] O. Kunert, M. Zitterbart, "Interconnecting fieldbuses through ATM", Local Computer Networks Proceedings, pp. 538-544, 1997.

- [16] I. Mizunuma, C. Shen, M. Takegaki, "Middleware for distributed industrial real-time systems on ATM networks", IEEE Real-Time Systems Symposium, pp. 32-38, 1996.

- [17] A.L. Chapin, "Standards for bridges and gateways", IEEE Network, Vol. 2, pp. 90-91, 1988.

- [18] M.M. Santos, D. Resende, O. Garzedin, P. Portugal, F. Vasques, "Technical and economical assessment of the use of wireless gateways in industrial networks", IECON: 2009 35th Annual Conference of IEEE Industrial Electronics, pp. 2357-2362, 2009.

- [19] E.G. Schmidt, M. Alkan, K. Schmidt, E. Yürüklü, U. Karakaya, "Performance evaluation of FlexRay/CAN networks interconnected by a gateway", Industrial Embedded Systems (SIES) 2010 International Symposium, pp. 209-212, 2010.

- [20] L. Seno, S. Vitturi, C. Zunino, "Analysis of Ethernet Powerlink wireless extensions based on the IEEE 802.11 WLAN", IEEE Transactions on Industrial Informatics, Vol. 5, pp. 86-98, 2009.

- [21] R. Lauckner, R. Rausch, P. Ribeiro, T. Wijnands, "A large scale flexible real-time communications topology for the LHC accelerator", Real Time Conference, IEEE NPSS, pp. 194-198, 1999.

- [22] WorldFIP, Home Page, available at: http://www.worldfip.org.

- [23] E. Tovar, F. Vasques, "Engineering real-time applications with WorldFIP: analysis and tools", SICICA, pp. 297-302, 2000.

- [24] P. Marino, M.A. Dominguez, F. Poza, F. Vazquez, "Using LOTOS in the specification of industrial bus communication protocols", Computer Networks, Vol. 45, pp. 767-799, 2004.

- [25] G. Liang, H. Wang, W. Li, D. Li, "Communication performance analysis and comparison of two patterns for data exchange between nodes in WorldFIP fieldbus network", ISA Transactions, Vol. 49, pp. 567-576, 2010.

- [26] A.V. Scott, W.J. Buchanan, "Truly distributed control systems using fieldbus technology", Seventh IEEE International Conference and Workshop on Engineering of Computer Based Systems, pp. 165-173, 2000.

- [27] E. Tovar, F. Vasques, "Distributed computing for the factory-floor: a real-time approach using WorldFIP networks", Computers in Industry, Vol. 44, pp. 11-31, 2001.

- [28] P. Marino, M.A. Dominguez, F. Poza, J.B. Nogueira, "Design of distributed system protocols based on standard FDL's", EUROMICRO Conference Proceedings, Vol. 2, pp. 334-341, 1999.

- [29] P. Marino, F. Poza, M.A. Dominguez, J.B. Nogueira, "Design of WorldFIP's industrial communication systems based on formal methods", Proceedings on the IEEE International Symposium on Industrial Electronics, Vol. 3, pp. 1427-1432, 1999.

- [30] J. Krupicka, A Short Introduction to ATM Concepts, Research Triangle Park, NC, USA, Wandel & Goltermann Technologies, Inc., 1996.

- [31] I.J. Hines, ATM: The Key to High-Speed Broadband Networking, New York, John Wiley, 1995.

- [32] 8285 Nways ATM Workgroup Switch Support, http://www.redbooks.ibm.com/redbooks/pdfs/sg244817.pdf

- [33] F. Hallsall, Data Communication, Computer Networks, Open Systems, 4th ed., Boston, Addison-Wesley, 1996.

- [34] W.J. Garrison, "NETWORK II.5 tutorial: network modeling without programming", Simulation Conference Proceedings, pp. 132-135, 1990.

- [35] CACI, Network II.5 User's Manual, Release 12, CACI Products Company, San Diego, 1997.