# Turkish Journal of Electrical Engineering & Computer Sciences

http://journals.tubitak.gov.tr/elektrik/

Research Article

Turk J Elec Eng & Comp Sci (2019) 27: 2456 - 2465 © TÜBİTAK doi:10.3906/elk-1812-143

## An analytical model to assess DC characteristics of independent gate Si FinFETs

Umer Faroog AHMED\*®, Muhammad Mansoor AHMED®

Department of Electrical Engineering, Capital University of Science and Technology, Islamabad, Pakistan

Received: 20.12.2018 • Accepted/Published Online: 05.05.2019 • Final Version: 26.07.2019

**Abstract:** In this paper, Poisson's equation is utilized to find the potential distribution inside the channel of an independent gate FinFET device by adding the effect of channel height. The channel height of the device plays an important role in surface potential calculation when top gate voltage is applied. Using surface potential, an I-V model is developed, which can find the device current both in linear and saturation regions of operation. The model is tested on devices of different dimensions and good agreement between modeled and simulated results is observed, which validates the authenticity of the proposed model.

**Key words:** Independent gate, FinFET, surface potential, I - V model

## 1. Introduction

FinFET is a promising new candidate for future technology due to its ability to control the channel of the device with relative ease compared to conventional FETs [1–3]. FinFETs are divided into two major categories depending on the gate of the device. Single gate FinFETs are controlled by one gate electrode while multiple gate FinFETs (MG-FinFETs) are controlled by more than one gate acting on the device independently [4, 5]. MG-FinFETs offer more flexibility in circuit design compared to single gate FinFETs.

MG-FinFETs are employed to control the threshold voltage [6], conversion gain [7], and power management [8] in large nano circuitries. Due to the 3-D structure of FinFETs, the height and effective width  $(W_{eff} = 2H_{fin} + T_{fin})$  of the device are always correlated and increasing one will also affect the other in a quantized fashion as all the fins must be of the same height due to the fabrication process limitations [9, 10]. Using MG-FinFETs, the width quantization effect on large circuits, such as SRAMs, can be reduced [11, 12]. Also, in independent gate SRAMs, the dual gate system acts as a built-in feedback network and reduces read/write margins [13, 14].

To fully comprehend the device behavior, models specific to independent gate FinFETs are needed. Researchers have developed many models for the characteristics of MG-FinFETs [15–17], but to the best of our knowledge, none of the models take into account the effect of channel height on the device characteristics. In this paper, a DC model is presented for MG-FinFETs by considering a 3-D field distribution inside the channel. Poisson's equation is solved to estimate the potential distribution inside the channel by taking into consideration the effect of channel height along with its length and width. By using drift equation and channel potential, current flowing through the device is calculated. The following sections describe the model formation

<sup>\*</sup>Correspondence: umerfarooq\_62@hotmail

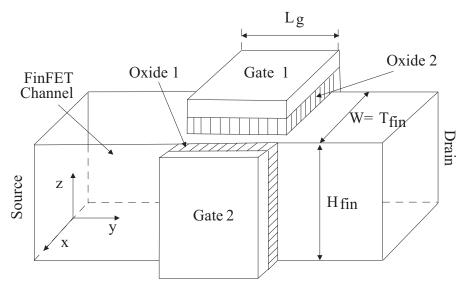

Figure 1. An independent gate FinFET device.

and the results obtained from it. A discussion is also presented on the basis of the results obtained and finally, conclusions associated with the study are summarized.

### 2. Model development

## 2.1. Surface potential model

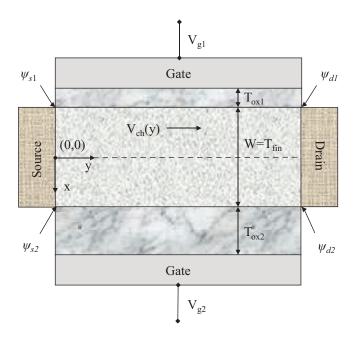

Figure 1 shows an independent multigate FinFET device. From the figure, it can be observed that two individual gate potentials are acting on the channel of the FinFET. This can easily be visualized from Figure 2, where the x-y cross-section of Figure 1 is illustrated.

Potential distribution inside the channel of a MG-FinFET can be expressed using Poisson's equation with appropriate boundary conditions. Poisson's equation, representing the potential distribution inside the channel taking into account both inversion and bulk charges, can be expressed as:

$$\frac{\partial^2 \psi_x}{\partial x^2} + \frac{\partial^2 \psi_z}{\partial z^2} = \frac{q n_i}{\epsilon_{si}} \exp\left(\frac{\psi + \phi_B - V_{ch}}{V_m}\right) + \frac{q N_a}{\epsilon_{si}},\tag{1}$$

where

$$\phi_B = V_m \ln \left( \frac{N_a}{n_i} \right), \tag{2}$$

and

$$V_m = \frac{kT}{q}. (3)$$

$V_{ch}(y)$ , shown in Figure 2, determines the drain-to-source potential at any given value of y, and it can vary from  $V_{ch}(0) = 0$  to  $V_{ch}(L_g) = V_{ds}$ . As channel depletion varies mostly in the x-direction, therefore:

$$\frac{\partial^2 \psi_z}{\partial z^2} \approx 0. {4}$$

Figure 2. Cross-sectional view of an independent gate FinFET device.

Eq. (4) can be integrated to get

$$\xi_z = \frac{\partial \psi_z}{\partial z} = \frac{V_{gs1}}{H_{fin}}$$

and  $\psi_z = \frac{V_{gs1}}{H_{fin}} z.$  (5)

Eq. (5) is attained by using boundary conditions

$$\psi_z(0,0,0) = 0$$

and  $\psi_z(0,0,H_{fin}) = V_{qs1}$ . (6)

Considering Eq. (1), the x-directed potential can be written as

$$\frac{\partial^2 \psi_x}{\partial x^2} = \frac{qn_i}{\epsilon_{si}} \exp\left(\frac{\psi + \phi_B - V_{ch}}{V_m}\right) + \frac{qN_a}{\epsilon_{si}},\tag{7}$$

subjected to boundary conditions

$$\frac{\partial \psi_x(x,y,z)}{\partial x}\bigg|_{x=z=0} = 0 \quad \text{and} \quad \psi_x(x=0,y,z=0) = \psi_0(y). \tag{8}$$

Integrating Eq. (7) and by applying boundary conditions given by Eq. (8), one can get

$$\xi_x = \frac{\partial \psi_x}{\partial x} = \left[ \frac{V_m q n_i}{\epsilon_{si}} \exp\left(\frac{\psi + \phi_B - V_{ch}}{V_m}\right) - \frac{V_m q n_i}{\epsilon_{si}} \exp\left(\frac{\psi_0 + \phi_B - V_{ch}}{V_m}\right) \right]^{1/2}. \tag{9}$$

The potential is applied on each gate independently; thus, it must be treated separately. Assuming that  $\psi_1$  is the potential due to  $V_{gs1}$  and  $\psi_2$  is the potential due to  $V_{gs2}$ , Eq. (9) can be written for both gates as

$$\xi_{x1} = \frac{\partial \psi_1}{\partial x} = \left[ \frac{V_m q n_i}{\epsilon_{si}} \exp\left(\frac{\psi_1 + \phi_B - V_{ch}}{V_m}\right) - \frac{V_m q n_i}{\epsilon_{si}} \exp\left(\frac{\psi_0 + \phi_B - V_{ch}}{V_m}\right) \right]^{1/2}, \tag{10}$$

and

$$\xi_{x2} = \frac{\partial \psi_2}{\partial x} = \left[ \frac{V_m q n_i}{\epsilon_{si}} \exp\left(\frac{\psi_2 + \phi_B - V_{ch}}{V_m}\right) - \frac{V_m q n_i}{\epsilon_{si}} \exp\left(\frac{\psi_0 + \phi_B - V_{ch}}{V_m}\right) \right]^{1/2}. \tag{11}$$

To eliminate the dependence of  $\xi_{x1}$  and  $\xi_{x2}$  on  $\psi_0(y)$ , both Eqs. (10) and (11) are squared and subtracted from each other, resulting in

$$\xi_{x1}^2 - \xi_{x2}^2 = \frac{V_m q n_i}{\epsilon_{si}} \exp\left(\frac{\psi_1 + \phi_B - V_{ch}}{V_m}\right) - \frac{V_m q n_i}{\epsilon_{si}} \exp\left(\frac{\psi_2 + \phi_B - V_{ch}}{V_m}\right). \tag{12}$$

By applying Gauss's law on both gates, the x-directed fields can be expressed as

$$\xi_{x1} = \frac{C_{ox1}}{\epsilon_{si}} [V_{gs1} - V_{fb1} - \psi_1] - \xi_z, \tag{13}$$

and

$$\xi_{x2} = \frac{C_{ox2}}{\epsilon_{ci}} [V_{gs2} - V_{fb2} - \psi_2], \tag{14}$$

where

$$C_{ox1} = \frac{\epsilon_{ox1}}{T_{ox1}}$$

and  $C_{ox2} = \frac{\epsilon_{ox2}}{T_{ox2}}$ . (15)

To find  $\psi_1$  and  $\psi_2$ , it is assumed that the potential  $\psi_2$  exists due to the weak inversion of carriers, and by using the capacitor distribution on both the gates,  $\psi_2$  can be evaluated as

$$\psi_2 = \alpha \psi_1 + \beta (V_{qs2} - V_{fb2}), \tag{16}$$

where

$$\alpha = \frac{C_{si}}{C_{si} + C_{ox2}}, \qquad \beta = \frac{C_{ox2}}{C_{si} + C_{ox2}}, \qquad C_{si} = \frac{\epsilon_{si}}{T_{fin}}.$$

(17)

In order to find  $\psi_1$ , Eqs. (12), (13), (14), and (16) are combined to get

$$\left(\frac{C_{ox1}}{\epsilon_{si}}[V_{gs1} - V_{fb1} - \psi_1] - \xi_z\right)^2 - \left(\frac{C_{ox2}}{\epsilon_{si}}[V_{gs2} - V_{fb2} - (\alpha\psi_1 + \beta(V_{gs2} - V_{fb2}))]\right)^2 - \frac{V_m q n_i}{\epsilon_{si}} \exp\left(\frac{\psi_1 + \phi_B - V_{ch}}{V_m}\right) + \frac{V_m q n_i}{\epsilon_{si}} \exp\left(\frac{\alpha\psi_1 + \beta\psi_1[V_{gs2} - V_{fb2}] + \phi_B - V_{ch}}{V_m}\right) = 0.$$

(18)

Eq. (18) can be solved iteratively to get the value of  $\psi_1$  and by putting  $\psi_1$  in Eq. (16),  $\psi_2$  is obtained.

#### 2.2. I-V model

The proposed I-V model utilizes drift equation and is given by

$$I_{ds} = 2\mu(V) \frac{W}{L_g} \int_0^{L_g} Q_{inv} \frac{\partial V_{ch}}{\partial y} \partial y.$$

(19)

The inversion charge can be expressed as

$$Q_{inv} = \epsilon_{si}(\xi_{x1} - \xi_{x2} + \xi_z) - Q_{bulk}, \tag{20}$$

where

$$Q_{bulk} = qN_ax. (21)$$

From Eq. (12),

$$\epsilon_{si}\xi_{x1} = \left[V_m q n_i \epsilon_{si} \left[\exp\left(\frac{\psi_1 + \phi_B - V_{ch}}{V_m}\right) - \exp\left(\frac{\psi_2 + \phi_B - V_{ch}}{V_m}\right)\right] + (\epsilon_{si}\xi_{x2})^2\right]^{1/2}.$$

(22)

Combining Eqs. (20) and (22), one can get

$$Q_{inv} = \left[ V_m q n_i \epsilon_{si} \left[ \exp\left(\frac{\psi_1 + \phi_B - V_{ch}}{V_m}\right) - \exp\left(\frac{\psi_2 + \phi_B - V_{ch}}{V_m}\right) \right] + (\epsilon_{si} \xi_{x2})^2 \right]^{1/2} - \epsilon_{si} \xi_{x2} + \epsilon_{si} \xi_z - Q_{bulk}.$$

$$(23)$$

Differentiating Eq. (23) w.r.t y,

$$\frac{\partial Q_{inv}}{\partial y} = \frac{1}{2V_m K_1} \left[ \gamma \exp\left(\frac{\psi_2 + \phi_B - V_{ch}}{V_m}\right) - \gamma \exp\left(\frac{\psi_1 + \phi_B - V_{ch}}{V_m}\right) \right] \frac{\partial V_{ch}}{\partial y} + \frac{1}{2V_m K_1} \left[ \gamma \exp\left(\frac{\psi_1 + \phi_B - V_{ch}}{V_m}\right) \frac{\partial \psi_1}{\partial y} - \gamma \exp\left(\frac{\psi_2 + \phi_B - V_{ch}}{V_m}\right) \frac{\partial \psi_2}{\partial y} \right], \tag{24}$$

where

$$K_1 = Q_{inv} + \epsilon_{si}\xi_{x2} - \epsilon_{si}\xi_z + Q_{bulk} \quad \text{and} \quad \gamma = V_m q n_i \epsilon_{si},$$

(25)

and also  $\partial \xi_{x2}/\partial y \approx 0$ . For a doped body,  $\psi_1, \psi_2 >> \psi_0$  and therefore Eqs. (10) and (11) can be rewritten as

$$\xi_{x1} \approx \sqrt{\frac{V_m q n_i}{\epsilon_{si}}} \exp\left(\frac{\psi_1(x, y, z) + \phi_B - V_{ch}(y)}{V_m}\right),$$

(26)

and

$$\xi_{x2} \approx \sqrt{\frac{V_m q n_i}{\epsilon_{si}}} \exp\left(\frac{\psi_2(x, y, z) + \phi_B - V_{ch}(y)}{V_m}\right).$$

(27)

Now, considering Eq. (23),

$$V_m q n_i \epsilon_{si} \left[ \exp\left(\frac{\psi_1 + \phi_B - V_{ch}}{V_m}\right) - \exp\left(\frac{\psi_2 + \phi_B - V_{ch}}{V_m}\right) \right] = K_2, \tag{28}$$

where,

$$K_2 = K_1^2 - (\epsilon_{si}\xi_{x2})^2. (29)$$

By using Eqs. (24), (26), (27), and (28),

$$Q_{inv}\frac{\partial V_{ch}}{\partial y} = \left(2V_m \frac{K_1}{K_2} \frac{\partial Q_{inv}}{\partial y} - \frac{K_3}{K_2} \frac{\partial \psi_1}{\partial y} + \frac{K_4}{K_2} \frac{\partial \psi_2}{\partial y}\right) Q_{inv},\tag{30}$$

where

$$K_3 = (\epsilon_{si}\xi_{x1})^2$$

and  $K_4 = (\epsilon_{si}\xi_{x2})^2$ . (31)

For simplicity,  $K_1/K_2 = \sigma_1$ ,  $K_3/K_2 = \sigma_2$ , and  $K_4/K_2 = \sigma_3$ . Now, by combining Eqs. (19) and (30), the drain-to-source current,  $I_{ds}$ , can be expressed as

$$I_{ds} = 2\mu(V)\frac{W}{L_g} \int_0^{L_g} \left(2V_m \sigma_1 \frac{\partial Q_{inv}}{\partial y} - \sigma_2 \frac{\partial \psi_1}{\partial y} + \sigma_3 \frac{\partial \psi_2}{\partial y}\right) Q_{inv} \partial y. \tag{32}$$

To simplify the above expression, it is approximated that the terms  $Q_{inv}$ ,  $\xi_{x2}$ , and  $\xi_z$  have their average values with respect to source and drain terminals, so

$$I_{ds} = 2\mu(V)\frac{W}{L_g} \left[ 2V_m \sigma_1(Q_{invd} - Q_{invs}) - \sigma_2(\psi_{1d} - \psi_{1s}) + \sigma_3(\psi_{2d} - \psi_{2s}) \right] \frac{Q_{invd} + Q_{invs}}{2}.$$

(33)

Eq. (33) gives the final expression of current, where  $Q_{invs}$  and  $Q_{invd}$  are the charges accumulated at the source and drain terminals of the FinFET, respectively.  $\psi_{1d}$  and  $\psi_{1s}$  are the drain and source potentials due to  $V_{gs1}$ , and  $\psi_{2d}$  and  $\psi_{2s}$  are the drain and source potentials due to  $V_{gs2}$ .

### 3. Results and discussion

To verify the validity of the proposed model, independent gate FinFETs of various dimensions were selected and their details are given in Table 1 [15, 18] and Table 2. Eq. (33) was used to plot the I-V characteristics of the FinFETs.

| Parameters                                   | $T_1$ [15] | $T_2$ [18] |

|----------------------------------------------|------------|------------|

| $L_g$ (nm)                                   | 100        | 10.8       |

| $T_{fin}$ (nm)                               | 15         | 4.5        |

| $H_{fin}$ (nm)                               | 30         | 12.5       |

| $H_{fin}/T_{fin}$                            | 2.0        | 2.8        |

| W (nm)                                       | 15         | 4.5        |

| $T_{ox1}$ (nm)                               | 2.0        | 0.61       |

| $T_{ox2} \text{ (nm)}$                       | 2.0        | 0.61       |

| $N_a \ (\times \ 10^{24} \ \mathrm{m}^{-3})$ | _          | 100        |

| $V_{th}$ (V)                                 | 0.5        | 0.3        |

**Table 1.** Physical parameters of independent gate FinFETs used in this study.

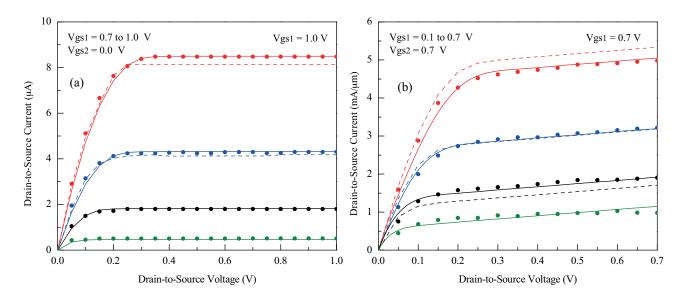

Figure 3a shows the result of the model against simulated data for the device having  $L_g = 100$  nm at  $V_{gs2} = 0$  V. Form the figure, it is evident that the proposed model can predict the characteristics of independent gate FinFETs with a high degree of accuracy. Figure 3b represents the I-V characteristics of the device having  $L_g = 10.8$  nm at  $V_{gs2} = 0.7$  V. From the plot, good agreement is observed between the modeled and simulated characteristics. From these figures, it is also evident that the proposed model can predict the I-V characteristics with reasonable accuracy when the applied bias and oxide thickness are varying. This confirms the validity of the proposed model, as it can anticipate the effect of changing  $V_{gs2}$  on the device characteristics.

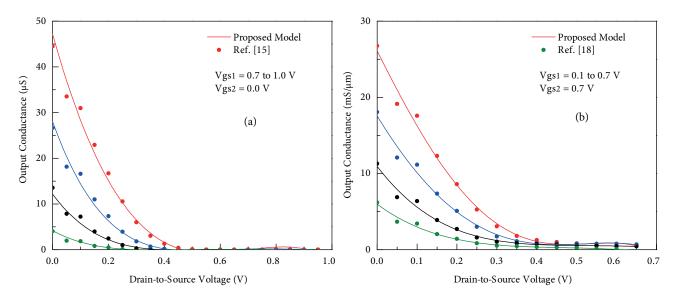

Figures 4a and 4b show the output conductance of devices  $T_1$  and  $T_2$ , respectively. By examining the figures, it can be seen that the proposed technique has the ability to accurately find the output conductance of

| Parameters                                             | Value           |

|--------------------------------------------------------|-----------------|

| $n_i \ (\times \ 10^{21} \ \mathrm{m}^{-3})$           | 1               |

| $k 	ext{ (J K}^{-1})$                                  | 1.38            |

| T(K)                                                   | 300             |

| $q \ (\times \ 10^{-19} \ \mathrm{C})$                 | 1.6             |

| $\mu  (\mathrm{m^2 V^{-1} s^{-1}})$                    | 0.11            |

| $\epsilon \; (\times \; 10^{-12} \; \mathrm{Fm}^{-1})$ | 8.85            |

| $\epsilon_{si}$                                        | $11.68\epsilon$ |

| $\epsilon_{ox1}$                                       | $3.9\epsilon$   |

| $\epsilon_{ox2}$                                       | $3.9\epsilon$   |

**Table 2.** Physical constants for independent gate FinFETs used in this study.

Figure 3. Comparison between modeled (solid line: proposed model with the effect of height, dashed line: model without the effect of height [15]) and simulated (dots) I - V characteristics of an independent gate FinFET with: a)  $L_g = 100 \text{ nm } (T_1)$  and b)  $L_g = 10.8 \text{ nm } (T_2)$ .

the devices, both in linear as well as in the saturation regions of operation, irrespective of the device dimensions and applied bias.

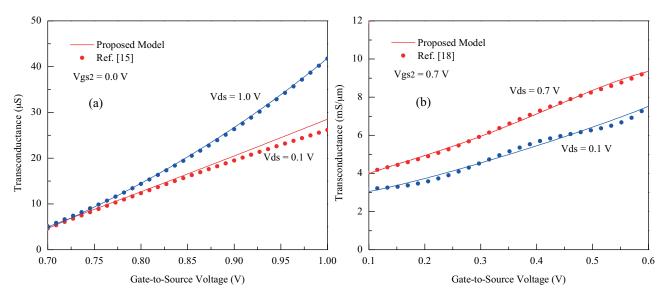

To study the response of the model for transfer characteristics, Figures 5a and 5b are plotted. The results of the figures show that the model is adequate in predicting the response of the device when the gate voltage is varied. For both linear and saturation regions, the model is equally valid and it also foresees the effect of back gate voltages on the transfer characteristics.

#### 4. Conclusion

In this paper, an I-V model for independent gate FinFETs is presented. The model uses the potential distribution inside the channel of the FinFET by solving Poisson's equation with appropriate boundary conditions.

Figure 4. Comparison between modeled and simulated output conductance of an independent gate FinFET with: a)  $L_q = 100$  nm and b)  $L_q = 10.8$  nm.

Figure 5. Comparison between modeled and simulated transfer characteristics of an independent gate FinFET with: a)  $L_g = 100$  nm and b)  $L_g = 10.8$  nm.

The surface potential acquired by Poisson's equation is used to derive the I-V expression. It has been shown that height of the fin plays an important role in the characteristics of FinFETs when top gate voltage is applied. The model is tested against independent gate FinFETs of varying dimensions, and it has been observed that the model predicts the effect of back gate voltage on the I-V characteristics of FinFETs with reasonable accuracy. This concurrence between the simulated and modeled results shows the validity of the proposed model and its potential use in simulation softwares.

#### Nomenclature

| x, y, z            | Rectangular coordinates         | $C_{si}$                           | Channel capacitor        |

|--------------------|---------------------------------|------------------------------------|--------------------------|

| $\psi(x,y,z)$      | 3-D surface potential           | $C_{ox1}, C_{ox2}$                 | Oxide capacitor          |

| q                  | Charge on electron              | $T_{ox1}, T_{ox2}$                 | Oxide thickness          |

| $n_i$              | Intrinsic carrier concentration | $\epsilon_{ox1}, \ \epsilon_{ox2}$ | Oxide permittivity       |

| $N_a$              | Doping concentration            | $\epsilon_{si}$                    | Permittivity of silicon  |

| $\phi_B$           | Device built-in potential       | $\mu(V)$                           | Field dependent mobility |

| $V_{ch}$           | Channel potential               | $L_g$                              | Gate length              |

| $V_{ds}$           | Drain-to-source voltage         | $\overline{W}$                     | Device width             |

| $V_{qs}$           | Gate-to-source voltage          | $T_{fin}$                          | Thickness of fin         |

| $V_{fb1}, V_{fb2}$ | Flat band voltages              | $H_{fin}$                          | Height of fin            |

| $\xi_x, \xi_z$     | x- and $z$ -directed fields     | $I_{ds}$                           | Drain-to-source current  |

### References

- [1] Ananthan H, Roy K. Technology and circuit design considerations in quasi-planar double-gate SRAM. IEEE T Electron Devices 2006; 53: 242-250.

- [2] Chen MC, Li KS, Li LJ, Lu AY, Li MY, Chang YH, Lin CH, Chen YJ, Hou YF, Chen CC et al. TMD FinFET with 4 nm thin body and back gate control for future low power technology. In: 2015 IEEE International Electron Devices Meeting; Washington, DC, USA; 2015. pp. 32.2.1-32.2.4.

- [3] Moroz V, Smith SL, Lu Q. FinFET with Heterojunction and Improved Channel Control. Google Patents 2016.

- [4] Fried DM, Duster JS, Kornegay KT. High-performance p-type independent-gate FinFETs. IEEE Electron Device Lett 2004; 25: 199-201.

- [5] Yang IY, Vieri C, Chandrakasan A, Antoniadis DA. Back-gated CMOS on SOIAS for dynamic threshold voltage control. IEEE T Electron Devices 1997; 44: 822-831.

- [6] Liu YX, Masahara M, Ishii K, Tsutsumi T, Sekigawa T, Takashima H, Yamauchi H, Suzuki E. Flexible threshold voltage FinFETs with independent double gates and an ideal rectangular cross-section Si-Fin channel. In: 2003 IEEE International Electron Devices Meeting; Washington, DC, USA; 2003. pp. 18.8.1-18.8.3.

- [7] Zhang W, Fossum JG, Mathew L, Du Y. Physical insights regarding design and performance of independent-gate FinFETs. IEEE T Electron Devices 2005; 52: 2198-2206.

- [8] Masahara M, Endo K, Liu YX, O'uchi S, Matsukawa T, Surdeanu R, Witters L, Doornbos G, Nguyen VH, Van den bosch G et al. Four-terminal FinFET device technology. In: 2007 IEEE International Conference on Integrated Circuit Design and Technology; Austin, TX, USA; 2007. pp. 1-4.

- [9] Kaur N, Rattan M, Gill SS. Impact of gate oxide thickness and aspect ratio of fin height and fin width on nanoscale tapered FinFETs. In: 2016 IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology; Bengaluru, India; 2016. pp. 1787-1791.

- [10] Nowak EJ, Aller I, Ludwig T, Kim K, Joshi RV, Chuang C, Bernstein K, Puri R. Turning silicon on its edge double gate CMOS/FinFET technology. IEEE Circuits Devices Mag 2004; 20: 20-31.

- [11] Tawfik SA, Liu Z, Kursun V. Independent-gate and tied-gate FinFET SRAM circuits: design guidelines for reduced area and enhanced stability. In: International Conference on Microelectronics; Cairo, Egypt; 2007. pp. 171-174.

- [12] Endo K, O'uchi SI, Ishikawa Y, Liu Y, Matsukawa T, Sakamoto K, Tsukada J, Ishii K, Yamauchi H, Suzuki E et al. Enhancing SRAM cell performance by using independent double-gate FinFET. In: 2008 IEEE International Electron Devices Meeting; San Francisco, CA, USA; 2008. pp. 1-4.

- [13] Guo Z, Balasubramanian S, Zlatanovici R, King TJ, Nikolić B. FinFET-based SRAM design. In: Proceedings of the 2005 International Symposium on Low Power Electronics and Design; San Diego, CA, USA; 2005. pp. 2-7.

### AHMED and AHMED/Turk J Elec Eng & Comp Sci

- [14] Ni H, Hu J, Yang H, Zhu H. Comprehensive optimization of dual threshold independent-gate FinFET and SRAM cells. Active and Passive Electronic Components 2018; 2018: 4512924.

- [15] Lu DD, Dunga MV, Lin CH, Niknejad AM, Hu C. A multi-gate MOSFET compact model featuring independent gate operation. In: 2007 IEEE International Electron Devices Meeting; Washington, DC, USA; 2007. pp. 565-568.

- [16] Hasan M, Gaillardon PE, Sensale-Rodriguez B. A continuous compact DC model for dual-independent-gate Fin-FETs. IEEE J Electron Devi 2017; 5: 23-31.

- [17] Datta A, Goel A, Cakici RT, Mahmoodi H, Lekshmanan D, Roy K. Modeling and circuit synthesis for independently controlled double gate FinFET devices. IEEE T Comput Aid D 2007; 26: 1957-1966.

- [18] Gupta SK, Kulkarni JP, Roy K. Tri-mode independent gate FinFET-based SRAM with pass-gate feedback: technology-circuit co-design for enhanced cell stability. IEEE T Electron Devices 2013; 60: 3696-3704.