Turkish Journal of Electrical Engineering & Computer Sciences

http://journals.tubitak.gov.tr/elektrik/

Turk J Elec Eng & Comp Sci (2020) 28: 3219 – 3234 © TÜBİTAK doi:10.3906/elk-1901-8

**Research Article**

# Design and application of SPWM based 21-level hybrid inverter for induction motor drive

Sheikh T. MERAJ<sup>1,\*</sup>, Kamrul HASAN<sup>2</sup>, Ammar MASAOUD<sup>3</sup>

<sup>1</sup>Department of Electrical and Electronics Engineering, Universiti Teknologi PETRONAS, Perak, Malaysia <sup>2</sup>Faculty of Electrical Engineering, Universiti Teknologi MARA, Selangor, Malaysia <sup>3</sup>Faculty of Mechanical and Electrical Engineering, Al-Baath University, Homs, Syria

| Received: 01.01.2019 • | Accepted/Published Online: 10.07.2020 | • | <b>Final Version:</b> 30.11.2020 |

|------------------------|---------------------------------------|---|----------------------------------|

|------------------------|---------------------------------------|---|----------------------------------|

Abstract: This paper presents the application of a newly developed 21-level hybrid multilevel inverter. A high frequency modulation technique known as sinusoidal pulse width modulation (SPWM) is applied to the hybrid inverter. This modulation methodology operates the switching sequences of the multilevel inverter to produce the desired 21-level output voltage. To validate the proper application of this inverter, it is further utilized to maintain the speed of a single phase induction motor. The velocity control of the motor is established on the principle of V/f control technique. The speed control strategy along with the compatibility of the SPWM modulation technique were verified by means of simulation and experimental results.

Key words: Power electronics, multilevel inverter, pulse width modulation, induction motor, speed control

## 1. Introduction

Power converter is a device which consists of a combination of semiconductor switches. These switches are designed to generate power by tuning its level and frequency in terms of load demand [1]. Despite its prevalent use, traditional inverters are not compatible in high voltage and high power applications. This phenomenon occurs due to the associated switching losses and power dissipations. Additionally, the conventional voltage source inverters generate nonsinusoidal voltage waveforms which are responsible for current distortion, diminishing motor efficiency and initiating unwanted vibrating torque. A significant drawback of conventional inverters is that they change the voltage step from zero to maximum voltage directly without any step change. This drawback can cause the breakdown of motor insulation due to the fast and frequent voltage rise known as dv/dt [2]. In order to overcome these drawbacks, researchers started improving the characteristics of conventional inverters and proposed the idea of multilevel inverters (MLIs). In contrast to conventional inverters, MLIs can change the output voltage in multiple steps rather than one step voltage change [3]. MLIs were primarily recommended for applications associated with high level voltage and power [4]. However, the applications of MLIs have been extended to other voltage levels due to its unique properties such as better waveform quality, less total harmonic distortion (THD) and lower switching losses [5]. Furthermore, the extensive applications of MLIs include adjustable speed drives, static VAR generation, power factor compensation etc. [6].

Multilevel inverters were first introduced in 1975 in the form of series connected H-bridge [7]. Since then various topologies of multilevel inverters have been developed and proposed by researchers. The three classic MLI topologies are neutral point clamped (NPC), flying capacitor (FC) and cascaded H-bridge (CHB) [8, 9].

<sup>\*</sup>Correspondence: meraj.tanzim@gmail.com

NPC inverters were primarily introduced in the industry as 3-level DC-MLI. A major concern of this type of inverter is the usage of high number of clamping diodes and capacitors to generate high voltage levels [10]. Unequal loss distribution among the power switches is an additional concern associated with these inverters [11]. A modified design of NPC, called active NPC (ANPC) has been proposed in 2005 to mediate the unequal loss distribution. This study utilized switches instead of clamping diodes to stabilize the losses among the switches [12]. FCs are also a type of conventional MLI which utilize different capacitors to produce high level of voltage. In case of FCs, more capacitors are required as the number of voltage levels increases. These capacitors can maximize the cost and minimize the reliability of the converter [13]. Finally, the CHB inverters are the latest traditional MLIs that have the minimum component count compared to NPC and FCs. As researchers are endeavouring to increase the number of voltage levels, several new topologies were proposed by modifying the fundamental MLIs. One of these modification is known as hybrid MLIs which are generally designed combining two or more MLI topologies. Some recently proposed hybrid topologies are discussed in [14-18]. The biggest advantages of the hybrid MLIs over the conventional MLIs are that; they have higher modularity with less power components, lower total harmonic distortions (THD), high voltage gains, simplicity in control and low common mode voltage (dv/dt). These features of the hybrid MLIs have made highly suitable in industrial motor drive applications. In addition, conventional MLIs change the voltage step from zero to maximum voltage usign lesser step and thus, create superfluous voltage stress on the switches and eventually decrease their longevity. It also causes the motor isolation to breakdown because of fast and frequent voltage rise which is known as common mode voltage. On the contrary, hybrid MLIs can change the output voltage in more voltage steps rather than lower voltage change and thus, significantly reduce the voltage stress on semiconductor switches. One of the most important specifications of hybrid MLIs is being able to control the voltage and frequency in between zero to maximal values by changing the supply frequency. Capability of limiting the negative effect of harmonics is another major specification of hybrid MLIs that can enhance the performance of AC drive. By implementing proper inverter control strategy, major harmonics frequency can be adjusted to a level in such a way that the inductive reactance of the motor can work as a filter keeping the distortion level in an acceptable limit.Conventional inverters lack these features resulting costly measures for instance, reduce the power rating of the motor and addition of filter. These deficiencies are sometime responsible for operational complication in motors like torque ripple or motor breakdown [19].

Considering all these facts stated above, this paper followed a new approach of generating high voltage levels by hybridizing a cross-switched MLI and a conventional full H-bridge inverter for induction motor drive utilizing fundamental frequency and speed control. A simplified sinusoidal pulse width modulation (SPWM) technique is implemented to control the hybrid MLI minimizing the common mode voltage, THD and increasing the transient response of the whole system. The operating principles of the proposed MLI and SPWM along with the implementation of V/f controller have been discussed in the following sections.

## 2. Hybrid MLI topology and its operation

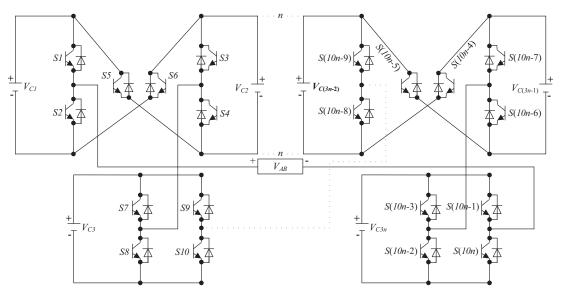

The proposed hybrid multilevel inverter is a combination of a cross switch inverter [20] containing six switches in conjunction with two DC supplies and a 3-level full H-bridge inverter consisting four switches with one DC supply. The middle two switches of the cross switched inverter denoted by S5 and S6 act as a channel between the two DC source voltage designated as  $V_{C1}$  and  $V_{C2}$ . The generated voltage from both DC sources is allocated in these two middle switches. Therefore, the voltage rating of these two switches will be high. The cross-switched inverter can produce 7-level output voltage within a range of +3E to -3E by using S1, S2, S3, S4, S5 and S6 switching combinations and maintaining a voltage ratio of 2:1 among the two DC sources  $V_{C1}$  and  $V_{C2}$ . Switches S1, S5 and S3 will function in complementary manner to switches S2, S4 and S6. The cross-switched inverter can be extended into  $N_{level}$  by following the equations stated below where  $n = 1, 2, 3, \dots$  and it represents the number of cell.

$$N_{Level} = (6n+1),\tag{1}$$

$$N_{Switch} = N_{Level} - 1, (2)$$

$$N_{DC\_supplies} = \frac{N_{Switch}}{3}.$$

(3)

Moreover, the H-bridge inverter can produce 3-level output voltage in a range of +E to -E utilizing the switching combination of S7, S8, S9 and S10. Switches S8 and S10 will function complementary to switches S7 and S9 respectively. The hybridization of these two inverters is capable of generating 21 voltage levels within a range of +10E to -10E. The final design of the hybrid inverter is illustrated Figure 1. In this case, the three DC sources designated as  $V_{C1}$ ,  $V_{C2}$  and  $V_{C3}$  follow a ratio of 2:1:7 among them. The complete switching configurations and their corresponding voltage levels are tabulated in Table 1. Similar to the cross-switched inverter the hybrid MLI can also be extended into  $N_{level}$  following Equations (4)–(6). It should be noted that to apply this extension the DC voltage sources should always follow 2:1:7 ratio among themselves.

$$N_{Level} = (20n+1),$$

(4)

$$N_{Switch} = \frac{N_{Level} - 1}{2},\tag{5}$$

$$N_{DC\_supplies} = \frac{3 \times N_{Switch}}{10}.$$

(6)

Figure 1. Schematic diagram of 21-level hybrid multilevel inverter.

| Switching states $(SW)$ | On/off switches |    |    |    |    | Output voltage $(\mathbf{V}_{\mathbf{AB}})$ |  |  |

|-------------------------|-----------------|----|----|----|----|---------------------------------------------|--|--|

|                         | <i>S1</i>       | S5 | S3 | S7 | S9 |                                             |  |  |

| 10                      | 1               | 0  | 0  | 1  | 0  | 10E                                         |  |  |

| 9                       | 1               | 0  | 1  | 1  | 0  | 9E                                          |  |  |

| 8                       | 0               | 0  | 0  | 1  | 0  | 8E                                          |  |  |

| 7                       | 1               | 1  | 0  | 1  | 0  | 7E                                          |  |  |

| 6                       | 1               | 1  | 1  | 1  | 0  | 6E                                          |  |  |

| 5                       | 0               | 1  | 0  | 1  | 0  | 5E                                          |  |  |

| 4                       | 0               | 1  | 1  | 1  | 0  | 4E                                          |  |  |

| 3                       | 1               | 0  | 0  | 0  | 0  | 3E                                          |  |  |

| 0                       | 1               | 0  | 0  | 1  | 1  |                                             |  |  |

| 2                       | 1               | 0  | 1  | 0  | 0  | 2E                                          |  |  |

| Ζ                       | 1               | 0  | 1  | 1  | 1  |                                             |  |  |

| 1                       | 0               | 0  | 0  | 0  | 0  | 1E                                          |  |  |

| 1                       | 0               | 0  | 0  | 1  | 1  |                                             |  |  |

| 0                       | 0               | 0  | 1  | 0  | 0  |                                             |  |  |

|                         | 0               | 0  | 1  | 1  | 1  | 0E                                          |  |  |

|                         | 1               | 1  | 0  | 1  | 1  |                                             |  |  |

|                         | 1               | 1  | 0  | 0  | 0  |                                             |  |  |

| -1                      | 1               | 1  | 1  | 0  | 0  | - <i>E</i>                                  |  |  |

| -1                      | 1               | 1  | 1  | 1  | 1  |                                             |  |  |

| -2                      | 0               | 1  | 0  | 0  | 0  | -2 <i>E</i>                                 |  |  |

| -2                      | 0               | 1  | 0  | 1  | 1  |                                             |  |  |

| -3                      | 0               | 1  | 1  | 0  | 0  | -3 <i>E</i>                                 |  |  |

| -0                      | 0               | 1  | 1  | 1  | 1  | -512                                        |  |  |

| -4                      | 1               | 0  | 0  | 0  | 1  | -4 <i>E</i>                                 |  |  |

| -5                      | 1               | 0  | 1  | 0  | 1  | -5 <i>E</i>                                 |  |  |

| -6                      | 0               | 0  | 0  | 0  | 1  | -6 <i>E</i>                                 |  |  |

| -7                      | 0               | 0  | 1  | 0  | 1  | -7 <i>E</i>                                 |  |  |

| -8                      | 1               | 1  | 1  | 0  | 1  | -8 <i>E</i>                                 |  |  |

| -9                      | 0               | 1  | 0  | 0  | 1  | -9 <i>E</i>                                 |  |  |

| -10                     | 0               | 1  | 1  | 0  | 1  | -10 <i>E</i>                                |  |  |

**Table 1**. Voltage levels and switching sequences of the 21-level hybrid MLI ( $V_{C1} = 2E, V_{C2} = E, V_{C3} = \tilde{\gamma}E$ ).

# 3. Sinusoidal pulse width modulation (SPWM)

The gate pulses and the 21-level output of the hybrid MLI are generated using level shifted SPWM technique as proposed in [21]. The method utilized in this paper follows a carrier wave arrangement where all the carrier waves above the zero reference are in phase but in opposite with those below zero reference. Since this inverter is capable of generating  $N_{Level} = 21$  voltage levels, it will require 20 carrier waves each having a frequency of  $f_{cr}$  and an amplitude of  $A_{cr}$ . Here, the reference signal is a sine wave which will be determined by the v/fcontrol algorithm. The frequency modulation index of the inverter and the amplitude modulation index are given by the following equations:

$$m_f = \frac{f_{cr}}{f},\tag{7}$$

$$m = \frac{A_m}{A_{cr} \times \frac{N_{Level} - 1}{2}}.$$

(8)

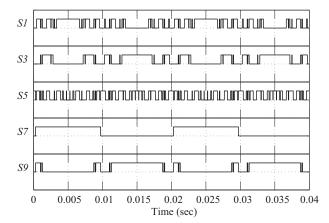

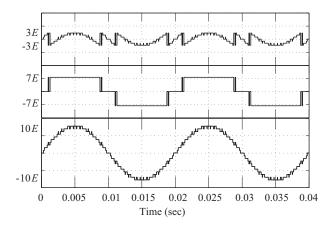

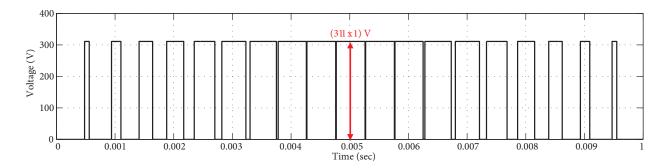

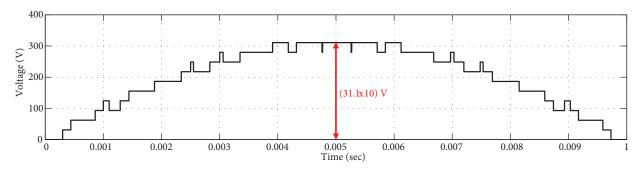

To execute the SPWM technique, the carrier signals above the zero reference and the carriers below the zero reference are identified initially. At every instant each carrier wave is compared with a modulating signal. For the positive carrier waves, if the modulating wave is greater than the carriers then the comparison will give '1' as an output and '0' for otherwise. On the other hand, for the negative carrier waves if the modulation wave is smaller than the carrier waves then the comparison will give '-1' as an output and '0' for otherwise. The pulses obtained from these comparisons are then added mathematically to acquire the switching states. Finally, 10 gate pulses are derived by comparing these switching states with the switching sequences of the proposed hybrid MLI as shown in Table 1. These gate pulses are further applied in the switches of the hybrid multilevel inverter to generate the simulation outputs as shown in Figures 2 and 3.

Figure 2. Gate pulses of the odd switches (S1, S3, S5, S7) and S9 of the hybrid MLI.

**Figure 3.** Branch voltages of: cross switch inverter  $(V_{C1} + V_{C2})$ , CHB  $(V_{C3})$  and hybrid MLI  $(V_{AB})$ .

## 4. Speed control of motor using v/f control

Generally, all the control strategies related to AC drives can be classified into two categories: scalar control methods and vector control methods. Based on this classification, this paper applies an open loop scalar control method known as constant voltage/frequency (V/f) control. In this control process, the stator voltage of the motor is maintained in proportion to the supply frequency. In electric drive system, the voltage/frequency (V/f) relation is linear when the motor speed is under the rated speed with little voltage offset. This indicates that at low frequency the THD is high with a low voltage amplitude. So the motor is least resistant to THD as the inductive reactance of harmonics filtering is proportional to the frequency. As a result, it is more effective to run the motor implementing linear pulse width modulation (PWM) which can control the effective harmonics frequency by setting carrier frequency.

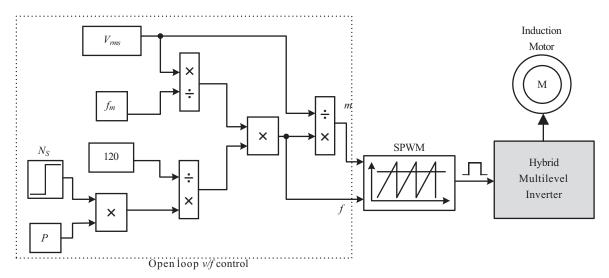

To maintain the speed of the motor effectively, the magnetic flux of the induction motor needs to be constant throughout the operation which is directly related to voltage and frequency. Therefore, the major objective of the proposed technique is to make sure the ratio of voltage to frequency is constant all the time so as to ensure constant airgap flux. It is important to maintain constant airgap flux to avoid saturation of stator and rotor core caused by the increase in flux when frequency or speed is decreased [17]. The saturation will lead to increase in the motor no load current which is undesirable. Hence, any change in frequency to achieve the reference motor speed will be accompanied by a change in the rms value of voltage. The schematic diagram of the v/f controller is shown in Figure 4.

Figure 4. Control diagram of the open loop v/f motor control technique.

The principle function of this controller is to calculate the required inverter output voltage frequency (f) and nominal modulation index (m) for achieving the user input reference synchronous speed  $(N_S)$ . The outputs of this controller are frequency (f) and modulation index (m) which is derived from  $(V_{rms})$ . The speed and frequency will change based on Equation (9) which is as follows:

$$N_S = \frac{120 \times f_m}{P}.\tag{9}$$

Here, P = 4 and it represents the number of pole of the induction motor whereas,  $f_m = 50$  Hz represents the nominal frequency of the single phase induction motor. For a newly varying synchronous speed, the corresponding change of frequency is calculated as follows:

$$f = \frac{P \times N_S}{120}.\tag{10}$$

#### 5. Simulation results

Simulation was done by deriving a sinusoidal reference wave having frequency f and modulation index m. Each carrier wave has a frequency of  $f_{cr} = 2000$  Hz and an amplitude of  $A_{cr} = 0.1$ . The hybrid MLI was built using three unequal DC supplies where,  $V_{C1} = 62.2$  V,  $V_{C2} = 31.1$  V and  $V_{C3} = 217.7$  V making the total DC supply voltage of the inverter to 311 V. However, the reference synchronous speed of the motor  $(N_S)$  was maintained from 1500 rpm to 1200 rpm to get the simulation results.

#### MERAJ/Turk J Elec Eng & Comp Sci

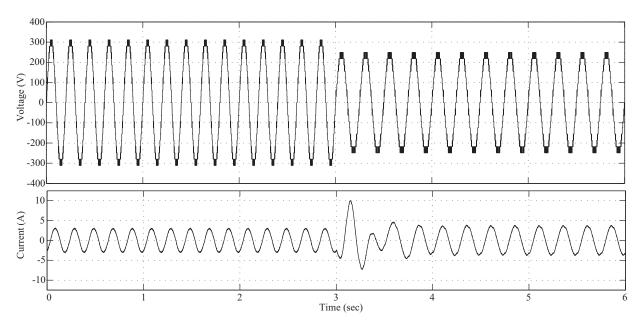

Since the reference synchronous speed of the motor  $(N_S)$  was changed at 3 s, the generated output voltage of the hybrid MLI has decreased from 21-level to 17-level which can be seen in Figure 5. This situation has occurred due to the change in both frequency and modulation index. During  $N_S = 1500$  rpm, the frequency was 50 Hz and the modulation index was m = 1. The step change has caused the motor speed to reduce to  $N_S = 1200$  rpm and the V/f controller converted the frequency to 40 Hz. As a result, the airgap flux have increased due to this sudden decreases in the frequency. In order to maintain the constant airgap flux, the controller decreases the voltage which causes the declination of the modulation index to m = 0.8.

Figure 5. Output voltage and current of the 21-level hybrid MLI during the speed change of the motor.

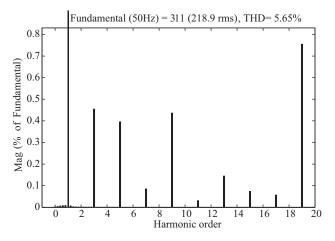

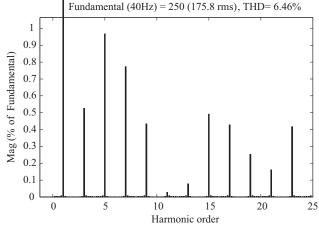

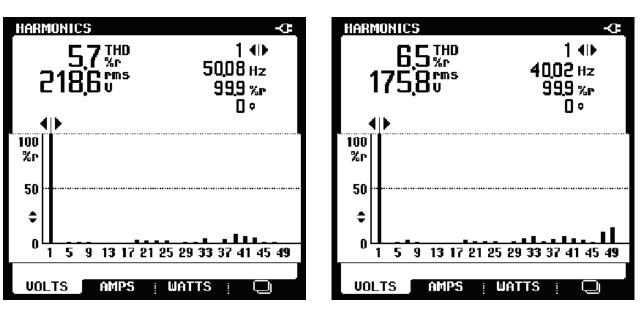

As shown in Figure 5, the output voltage was initially  $V_{AB\_max} = 311$  V consisting of 21 levels. However, at 3 s, when the step changed occurred the output voltage immediately decreased to  $V_{AB} = 250$  V generating 17 levels. Similarly, it can be observed from Figures 6 and 7 that the RMS voltage have also declined from  $V_{AB\_rms} = 218.9$  V to  $V_{AB\_rms} = 175.8$  V. Theoretically, the RMS value can be calculated from the following equation:

$$V_{ABrms} = 0.707 \times m \times V_{ABmax}.$$

(11)

Additionally, it can be observed from the harmonic spectrum of Figures 6 and 7 that the THD has increased from 5.65% to 6.46%. This happened due to the lower voltage steps produced from the hybrid topology after the step change of the motor has occurred.

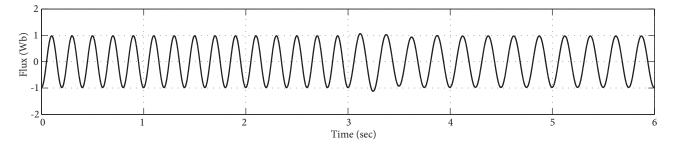

The main objective of the V/f control is to keep the stator flux of the motor constant. It is clear from the well known fact that the frequency of the system decreases along with the motor speed. Therefore, during speed change from 1500 rpm to 1200 rpm, the frequency decreases to 40 Hz from 50 Hz. It should be noted that in constant V/f control, until the rated speed of the motor, the motor flux will remain constant. It can be observed from Figure 8 that even after the step change, the flux remains unchanged. Thus, it can be concluded that the V/f control method implemented in this paper is successful.

Figure 6. Harmonic spectrum before step change at m = 1 and  $N_S = 1500$  rpm.

Figure 7. Harmonic spectrum after step change at m = 0.8 and  $N_S = 1200$  rpm.

Figure 8. Constant stator flux during the step change of the motor.

## 6. Experimental results

To validate the concept of proposed 21-level hybrid inverter and verify the simulation results, the prototype of the inverter was designed using TMS320F28335 digital signal processor (DSP). The gate drivers are isolated using different output ports from the DSP. These output ports will provide specific gate signals for specific gate drivers. For instance, output port 1 of DSP will only provide the gate signal for gate driver 1. Thus, gate driver 1 will only be able to provide gate pulses for S1 switch of the hybrid MLI. The DC link was built following an asymmetrical configuration where  $V_{C1} = 62.2$  V,  $V_{C2} = 31.1$  V and  $V_{C3} = 217.7$  V and  $V_{AB} = 311$  V. Thus, a voltage ratio of 2:1:7 among the DC supplies was ensured. This particular voltage configuration was followed to meet the minimum DC voltage requirement of the single phase induction motor. The complete hardware specification of the prototype is given in Table 2.

In order to investigate the performance of the proposed inverter, a single phase capacitor run capacitor start induction motor was connected. The constant V/f control was implemented by using SPWM control technique as discussed in Section 3. Therefore, using the principle of SPWM operation, the hybrid MLI will produce a single phase output to run the motor.

The purpose of this experimental test was to evaluate the performance of the proposed inverter by driving the motor at different reference speeds. In this section, the experiment was conducted following two modes of operation. The fist mode of operation represents the state prior to the step change while the second mode of

| Hardware specification | Symbol        | Value/model         |

|------------------------|---------------|---------------------|

|                        | $V_{C1}$      | 62.2 V              |

| DC voltage supplies    | $V_{C2}$      | 31.1 V              |

|                        | $V_{C3}$      | 217.7 V             |

| Switching frequency    | $f_S$         | 2000 Hz             |

| Motor power            | Р             | 300 W               |

| Motor pf               | θ             | 0.89                |

| Motor current          | Ι             | 2.42 A              |

| IGBT switches          | <i>S1-S10</i> | Fuji 2MBI150U2A-060 |

| IGDI SWITCHES          |               | 150 A and 600 V $$  |

| Gate drive optocoupler |               | HCPL3120            |

| Gate drive IC          |               | SN7411C04N          |

Table 2. Specifications of the hardware prototype.

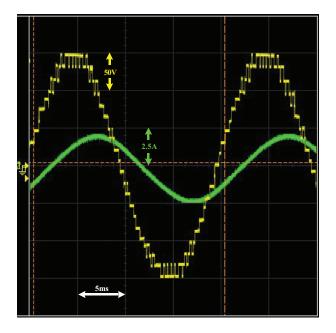

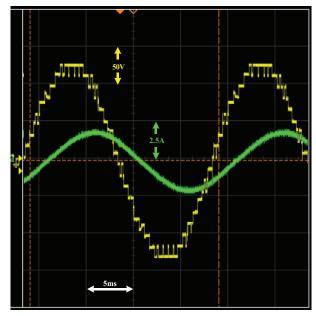

operation represents the state after the step change was applied. Figure 9 demonstrates the output voltage during the first mode of operation when the motor was running at a rated speed,  $N_S = 1500$  rpm having a fundamental frequency, f = 50 Hz and modulation index, m = 1. In this state, the inverter generated the maximum output voltage,  $V_{AB\_max} = 311$  V consisting 21-levels. However, in the second mode of operation, the speed of the induction motor was decreased to  $N_S = 1200$  rpm. The fundamental frequency and the modulation index were also decreased to f = 40 Hz and m = 0.8 respectively as shown in Figure 10. In this post step change state, the proposed inverter produced output voltage  $V_{AB} = 250$  V generating 17-levels instead of 21-levels. By observing Figure 11, it can be stated that the inverter's RMS voltage was  $V_{AB\_rms} = 218.6$  V initially and it also has a lower dv/dt ratio with a total harmonic distortion (THD) of 5.7%. Moreover, during the second mode of operation, the RMS voltage was reduced to  $V_{AB\_rms} = 175.8$  V. This also showed a higher dv/dt ratio with an increased THD of 6.5% as illustrated in Figure 12.

#### 7. Comparative analysis

As mentioned earlier, one of the major drawback of multilevel inverter is the demand of high number of power electronic elements. To evaluate the characteristics of the proposed topology, the inverter is compared with the traditional inverters such as asymmetrical CHB, NPC, FC and recently developed MLI topologies [22–27] in terms of required number of power electric components. The comparative analysis is displayed in Table 3. It can be observed that the proposed inverter significantly minimizes the required number of switches, DC voltage supplies, diodes, flying capacitors and DC bus capacitors. In comparison with the other MLI topologies, the major advantages of the proposed 21-level MLI are: (i) High number of voltage level with less number of power electronic components (ii) The proposed inverter combines the advantage of cross-switch MLI and traditional Hbridge inverter which include simple operation technique, minimized power components and low THD. (iii) The hybrid inverter is compatible with the proposed high frequency SPWM modulation technique. The compatibility was validated by obtaining similar and accurate results in both simulation and experimental sections. The technique was successfully applied to produce appropriate switching signals and operate the inverter in both high and low modulation indices. It is worth mentioning that the proposed modulation technique utilized in this paper can be implemented for all types of multilevel inverters. On the contrary, the only disadvantage of

### MERAJ/Turk J Elec Eng & Comp Sci

Figure 9. Experimental output voltage and current before step change at m = 1 and  $N_S = 1500$  rpm.

Figure 10. Experimental output voltage and current before step change at m = 0.8 and  $N_S = 1200$  rpm.

Figure 11. Experimental harmonic spectrum before step change at m = 1 and  $N_S = 1500$  rpm.

Figure 12. Experimental harmonic spectrum after step change at m = 0.8 and  $N_S = 1200$  rpm.

the proposed hybrid inverter is the use the of cross connected semiconductor switches. The voltage rating of the semiconductor switches is high since these switches have to share voltages from two DC supplies. Therefore, switches that can withstand high voltage is required to be used which can increase the overall cost of the system.

The superiority of the proposed hybrid inverter is further proven by its motor drive application with a conventional 3-level CHB inverter and five other recently developed MLIs proposed in [15–17, 25, 27]. It

| Inverter types               | Switches | DC supplies | DC bus     | Flying     | Diodes | Total      |

|------------------------------|----------|-------------|------------|------------|--------|------------|

|                              |          | DC supplies | capacitors | capacitors | Dioues | components |

| Neutral point clamped        | 40       | 1           | 20         | 0          | 60     | 121        |

| Flying capacitors            | 40       | 1           | 20         | 28         | 40     | 128        |

| Symmetrical CHB              | 40       | 10          | 0          | 0          | 40     | 90         |

| Asymmetrical CHB             | 12       | 3           | 0          | 0          | 12     | 27         |

| Cross-switched MLI [22]      | 40       | 1           | 20         | 0          | 60     | 121        |

| Reduced switched MLI [23]    | 16       | 5           | 0          | 0          | 16     | 37         |

| Switch ladder MLI [24]       | 10       | 4           | 0          | 0          | 10     | 24         |

| Asymmetrical hybrid MLI [25] | 12       | 3           | 3          | 0          | 12     | 30         |

| Switched-capacitor MLI [26]  | 16       | 1           | 0          | 20         | 36     | 72         |

| Symmetrical hybrid MLI [27]  | 10       | 1           | 7          | 0          | 10     | 28         |

| Proposed topology            | 10       | 3           | 0          | 0          | 10     | 23         |

Table 3. Comparison between different MLI topologies in terms of power electric components.

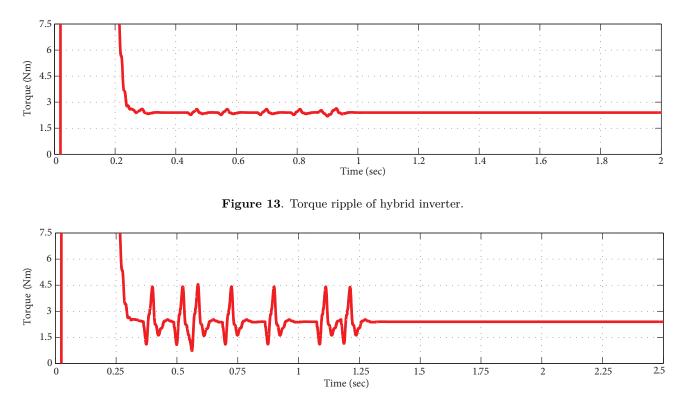

should be mentioned that the for the MLI proposed in [27], 11-level model (highest end) is considered for the comparison. Graphical comparisons are given only while comparing with the conventional CHB inverter whereas, numerical values were shown when comparing with the hybrid MLIS. In other words, the comparative approach is demonstrated considering the graphical comparison (with CHB) as a highest benchmark (100%). The comparison is done in terms of torque ripple, transient response, dv/dt ratio and total harmonic distortions. Figure 13 shows the torque waveform for the hybrid inverter while Figure 14 shows the torque waveform for the CHB inverter. By comparing these figures it can be clearly stated that the hybrid inverter produced torque waveform with significantly lesser ripples than CHB inverter. In other words, it produced only 5.5%ripples compared to CHB inverter. Besides, the topology proposed in [15] produced 27.75% whereas, the hybrid topologies [16, 17, 25, 27] produced torque ripple of almost 86.85%, 64.61%, 33.23% and 54.5% respectively. Furthermore, it can be seen that the waveform of the hybrid inverter became ripple free after 0.9 s whereas, the waveform of the CHB inverter got ripple free at 1.25 s. Thus, proposed MLI showed 0.35 s faster transient response compared to the CHB inverter. Putting matter into similar perspectives, the other hybrid MLIs got ripple free at 0.995 s, 1.205 s, 1.129 s, 1.014 s and 1.099 s respectively. Therefore, it proves that the settling time of hybrid inverter is also better than CHB inverter and all other hybrid MLIs mentioned in this section. This comparison provides a greater advantage for the proposed inverter over the other MLIs since, increased torque ripple can induce torsional oscillation and damage motor's shaft.

Figures 15 and 16 show the common mode voltage of the the conventional CHB and the hybrid MLI respectively. For H-bridge inverter, the switches produce output lines in between zero and maximum voltage which causes high and repetitive fast voltage rise. Due to this switches can be melt down or fused. However, in case of hybrid MLI, the voltage step is very low and it is only 10% of the maximum voltage. Considering the similar aspect, the hybrid MLIs [15–17, 25, 27] produced voltage steps which are 18.29%, 62.2%, 35.56%, 20.73% and 28.27% of the maximum voltage (311 V). This low voltage step of the proposed MLI compared to other MLIS, ensures low dv/dt and decreases electromagnetic interference (EMI). For inverter fed motor drives, high dv/dt in the output voltage of the inverter can create partial discharging which is responsible for premature failure of motor winding insulation. Because of high dv/dt, bearing current is produced by the shaft voltages

Figure 14. Torque ripple of CHB inverter.

flowing into the shaft bearing resulting in early bearing failure. It can also create voltage reflections in the cable which can increase the motor terminal voltage, maximize the ground currents and eventually decrease the lifetime of the motor [21].

The total harmonic distortions (THD) of all the hybrid MLIs including the conventional CHB inverter are obtained by establishing similar simulation parameters and control. The input DC-link voltage of all these inverters are considered to be 31.1 V with the gate pulses generated by applying SPWM technique as discussed earlier. These information are further tabulated in Table 4 for better understanding. It can be addressed that the proposed MLI has generated significantly better harmonic profile compared to all other MLIs. From the aforementioned analysis, the advantages of the proposed hybrid MLI can be listed as follows: (i) it can produce higher voltage level employing reduced power components, (ii) it does not create any voltage imbalance since, it does not require the use of clamping diodes or flying capacitors, (iii) its operating principleis very simple and can be related to conventional CHB inverter, (iv) it can perform better industrially since, it produces lower torque ripples, lower common mode voltage, has faster transient response and has a better harmonics profile.

## 8. Power loss calculation and efficiency

To calculate the power loss of the proposed module, the total DC-link voltage of 1300 V and a load of (237  $\Omega$  0.53 H) were considered. Thus, the proposed MLI can deliver 3.5 kW output power (0.98 W/s). In this experiment, Fuji 2MBI150U2A-060 model of IGBTs are utilized. Two principle losses generally occur during the operation of switching devices. These losses are classified as conduction losses and switching losses. Conduction losses ( $P_{Conduction}$ ) are defined as the losses of power electronic devices during on-state. In this case, both

Figure 15. Common mode voltage of CHB inverter.

Figure 16. Common mode voltage of 21-level hybrid inverter.

| Parameters               | CHB   | [15]  | [16]  | [17]  | [25]  | [27]  | Proposed |

|--------------------------|-------|-------|-------|-------|-------|-------|----------|

| Torque ripple (%)        | 100   | 27.75 | 86.85 | 64.61 | 33.23 | 54.5  | 5.5      |

| Transient response (sec) | 1.25  | 0.995 | 1.205 | 1.129 | 1.014 | 1.099 | 0.9      |

| Common mode voltage (%)  | 100   | 18.29 | 62.2  | 35.56 | 20.73 | 28.27 | 10       |

| THD (%)                  | 51.89 | 6.45  | 17.26 | 13.77 | 8.78  | 11.06 | 5.65     |

Table 4. Comparison between different MLI topologies in terms of performance.

diode and the switches are taken into consideration. The instantaneous conduction losses of the IGBT and diodes can be determined using Equations (12) and (13), respectively.

$$IGBT(t) = [V_{IGBT} + R_{IGBT}i(t)] \times i(t) = 7.27 \text{mW/s.}$$

$$(12)$$

$$Diode(t) = [V_{Diode} + R_{Diode}i(t)] \times i(t) = 2.49 \text{mW/s}.$$

(13)

Here,  $V_{IGBT}$  and  $V_{Diode}$  are the on-state voltage of the switches and diodes respectively.  $R_{IGBT}$  and  $R_{Diode}$  represents the equivalent resistance of the switches and the diodes. Using Equations (12) and (13) losses of each device is calculated and these results are added together to determine the conduction losses of the hybrid MLI.

Switching losses ( $P_{Switching}$ ) are defined as the losses of power electronic devices during them turn on and turn off. Similar to previous case, these losses are calculated for both switches and the antiparallel diodes. This loss is directly proportional to the switching frequency. The turn on  $(E_{on})$  and turn off  $(E_{off})$  energy loss of x switching devices can be calculated as follows:

$$E_{on,x} = \int_0^{t_{on}} \left[ \left( \frac{v_{switch,x}}{t_{on}} t \right) \left( -\frac{I}{t_{on}} (t - t_{on}) \right) \right],\tag{14}$$

$$E_{off,x} = \int_0^{t_{off}} \left[ \left( \frac{v_{switch,x}}{t_{off}} t \right) \left( -\frac{I}{t_{off}} (t - t_{off}) \right) \right].$$

(15)

Here,  $t_{on}$  and  $t_{off}$  is the turn on time and turn off time of the switches consecutively. I represents the current through the IGBT devices before/after they are turned off/on.  $v_{switch,x}$  demonstrates the forward voltage drop of x switch. Thus,

$$P_{Switching} = f \left[ \sum_{x=1}^{N_{switch,x}} \left( \sum_{i=1}^{N_{on,x}} E_{on,xi} + \sum_{i=1}^{N_{off,x}} E_{off,xi} \right) \right] = 3.75 \text{mW/s.}$$

(16)

Where, f is the fundamental frequency,  $N_{on,x}$  and  $N_{off,x}$  represents the number of times x switch is turned on and off during a time period of t. In addition,  $E_{on,xi}$  is the energy loss of x switch turning on for ith time whereas,  $E_{off,xi}$  is the energy loss of x switch turning off for ith time. Thus, the total loss ( $P_{Total}$ ) and efficiency can be calculated as follows:

$$P_{Total} = P_{Conduction} + P_{Switching} = 13.51 \text{mW/s.}$$

(17)

$$\eta = \frac{P_{out}}{P_{Total} + P_{out}} \times 100 = 96.64\%.$$

(18)

#### 9. Conclusion

This paper introduced the complete design and application of a single phase 21-level hybrid multilevel inverter utilizing less number of power electronic components. It has been demonstrated that the proposed inverter is capable of operating at different modulation indices for motor drive application. The high frequency sinusoidal pulse width modulation technique was precisely implemented for two modes of operation: 21-level and 17-level. In both modes, the proposed inverter generated high quality voltage waveforms and was able to control the speed of the motor effectively. It should also be noted that, despite using high frequency modulation technique, the total harmonic distortions of the voltage waveforms were considerably low. Finally, the feasibility of the proposed inverter and the reliability of the implemented modulation technique were verified. This can also be confirmed from the simulation and experimental results for the AC induction motor which showed a close agreement.

#### References

- [1] Trzynadlowski A. Introduction to Modern Power Electronics. 2nd ed. New York, NY, USA: Wiley, 1998.

- [2] Winter FD, Wu B. Medium voltage motor harmonic heating, torques and voltage stress when applied on VFDs. In: IAS Petroleum and Chemical Industry Technical Conference; Philadelphia, USA; 1996. pp. 131-139.

- [3] Rashid M. Power Electronics Handbook: Devices, Circuits, and Applications. 3rd ed. Cambridge, MA, USA: Elsevier Inc., 2011.

- [4] Marchesoni M. High-performance current control techniques for application to multilevel high-power voltage source inverters. IEEE Transactions on Power Electronics 1992; 7 (1): 189-204.

- [5] Chaturvedi P, Jain S, Agrawal P, Nema R, Sao K. Switching losses and harmonic investigations in multilevel inverters. IETE Journal of Research 2008; 54 (4): 297.

- [6] Rodriguez J, Lai JS, Peng FZ. Multilevel inverters: a survey of topologies, controls, and applications. IEEE Transactions on Industrial Electronics 2002; 49 (4); 724-738.

- [7] Baker RH, Lawrence HB. Electric Power Converter. U.S. Patent Number 3,867,643, 1975.

- [8] Malinowski M, Gopakumar K, Rodriguez J, Perez M. A survey on cascaded multilevel inverters. IEEE Transactions on Industrial Electronics 2010; 57 (7): 2197-2206.

- [9] Pulikanti S, Konstantinou G, Agelidis V. Generalization of flying capacitor-based active-neutral-point-clamped multilevel converter using voltage-level modulation. IET Power Electronics 2012; 5 (4): 456.

- [10] Rodriguez J, Bernet S, Steimer P, Lizama I. A survey on neutral-point-clamped inverters. IEEE Transactions on Industrial Electronics 2010; 57 (7): 2219-2230.

- [11] Meraj ST, Hasan K, Masaoud A. A novel configuration of cross-switched T-type (CT-Type) multilevel inverter. In: IEEE Transactions on Power Electronics 2020; 35 (4): 3688-3696.

- [12] Bruckner T, Bernet S, Guldner H, The active NPC converter and its loss-balancing control. IEEE Transactions on Industrial Electronics 2005; 52 (3): 855-868.

- [13] Wang H, Blaabjerg F. Reliability of capacitors for dc-link applications in power electronic converters: an overview. IEEE Transactions on Industrial Applications 2014; 50 (5): 3569-3578.

- [14] Pulikanti S, Agelidis V. Hybrid flying-capacitor-based active- neutral-point-clamped five-level converter operated with SHE-PWM. IEEE Transactions on Industrial Electronics 2011; 58 (10): 4643-4653.

- [15] Kumar P, Kaarthik R, Gopakumar K, Leon J, Franquelo L. Seventeen-level inverter formed by cascading flying capacitor and floating capacitor H-bridges. IEEE Transactions on Power Electronics 2015; 30 (7): 3471-3478.

- [16] Adam G, Salam IA, Ahmed K, Williams B. Hybridmultilevel converter with cascaded h-bridge cells for HVDC applications: Operating principle and scalability. IEEE Transactions on Power Electronics 2015; 30 (1): 65-77.

- [17] Zheng Z, Wang K, Xu L, Li Y. A hybrid cascaded multilevel converter for battery energy management applied in electric vehicles. IEEE Transactions on Power Electronics 2014; 29 (7): 3537-3546.

- [18] Rajeevan P, Gopakumar K. A reduced device-count hybrid multilevel inverter topology with single dc source and improved fault tolerance. European Power Electronics and Drives 2013; 23 (2): 14-23.

- [19] Rajeevan P, Sivakumar K, Gopakumar K, Patel C, Abu-Rub H. A nine-level inverter topology for medium-voltage induction motor drive with open-end stator winding. IEEE Transactions on Industrial Electronics 2013; 60 (9): 3627-3636.

- [20] Meraj ST, Hasan K, Masaoud A. Simplified one dimensional space vector modulation of cross-switched multilevel inverter. In: IEEE Student Conference on Research and Development; Putrajaya, Malaysia; 2017. pp. 350-355.

- [21] Meraj ST, Law KH, Masaoud A. Simplified sinusoidal pulse width modulation of cross-switched multilevel inverter. In: IEEE 15th International Colloquium on Signal Processing and Its Applications; Penang, Malaysia; 2019. pp. 1-6.

- [22] Kangarlu MF, Babaei E. Cross-switched multilevel inverter: an innovative topology. IET Power Electronics 2013; 6 (4): 642-651.

- [23] Jayabalan M, Jeevarathinam B, Sandirasegarane T. Reduced switch count pulse width modulated multilevel inverter. IET Power Electronics 2017; 10 (1): 10-17.

- [24] Alishah RS, Hosseini SH, Babaei E, Sabahi M. Optimal design of new cascaded switch-Ladder multilevel inverter structure. IEEE Transactions on Industrial Electronics 2017; 64 (3): 2072-2080.

- [25] Nami A, Zare F, Ghosh A, Blaabjerg F. A hybrid cascade converter topology with series-connected symmetrical and asymmetrical diode-clamped H-bridge cells. IEEE Transactions on Power Electronics 2011; 26 (1): 51-65.

## $\rm MERAJ/Turk$ J Elec Eng & Comp Sci

- [26] Babaei E, Gowgani SS. Hybrid multilevel inverter using switched capacitor units. IEEE Transactions on Industrial Electronics 2014; 61 (9): 4614-4621.

- [27] Gautam SP, Gupta S, Kumar L. Hybrid topology of symmetrical multilevel inverter using less number of devices. IET Power Electronics 2015; 8 (11): 2125-2135.